В.С. Бурцев

Параллелизм вычислительных процессов и

развитие архитектуры суперЭВМ

### <u>В.С.Бурцев</u>

Параллелизм вычислительных

процессов и развитие

архитектуры

суперЭВМ

Москва 1997

### Всеволод Сергеевич Бурцев

Параллелизм вычислительных процессов и развитие архитектуры суперЭВМ M, 1997

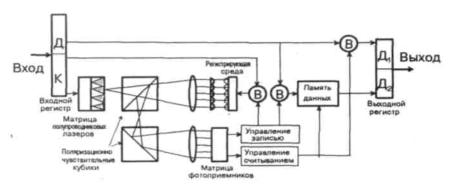

В книге представлена часть трудов академика Всеволода Сергеевича Бурцева, написанных им за период с 1993 по 1996 годы. Часть работ публикуется впервые. В работах прослеживается основное направление исследований создание нетрадиционных высокопараллельных архитектур вычислительных машин и комплексов с использованием новых физических принципов, в частности, оптических и оптоэлектронных устройств.

В настоящее время средства обработки информации переживают бурное развитие. Немаловажным является тот интересный факт, что в каких бы областях науки и техники не использовались различные средства обработки информации, в конечном счете, требования к их развитию сводятся, так или иначе, к одному - увеличению производительности вычислительных средств при уменьшении потребляемой мощности и повышению надежности. Этим, наверное, объясняется то обстоятельство, что архитектурные и схемотехнические решения, принятые в суперЭВМ ЭВМ. обладающих наибольшей производительностью на фиксированный момент времени, определяют передний фронт развития этой отрасли.

Увеличение производительности обработки информации, в основном, достигается двумя путями: первый - увеличением быстродействия элементной базы, включая конструкцию, и второй - архитектурными решениями построения средств обработки информации. Первый путь практически исчерпал все возможности и дальнейшее продвижение в этом направлении требует открытия новых физических принципов обработки информации.

Второй путь, в основе которого лежит распараллеливание процессов обработки информации на всех уровнях решения задачи, широко использовался на всех этапах развития информационно-вычислительных средств:

- переход от последовательного счета к параллельному;

- параллельная работа основных устройств ЭВМ;

- введение пакетного режима работы и режима разделения времени;

- мультиплексный режим обработки данных;

- конвейерный режим;

- многопроцессорные и многомашинные комплексы;

- режим управления потоками данных и т. д.

Второй путь повышения производительности обработки информации на настоящее время далеко не исчерпал себя и с успехом будет развиваться в перспективных суперЭВМ.

Можно с уверенностью сказать, что развитие архитектуры суперЭВМ идет в направлении создания условий для выявления и реализации параллельных процессов на всех уровнях взаимодействия человека с суперЭВМ.

Этим обстоятельством и объясняется название данной книги, в которой собраны статьи, написанные в 1993-1996 г.г., опубликованные в различных журналах и сборниках, а также вновь подготовленные к печати. В них прослеживаются вышеприведенные тенденции развития вычислительной техники и предлагаются методы их реализации на современном этапе.

Сборник составлен на базе опыта многолетней работы совместно с большим коллективом сотрудников, из которых особую благодарность автор выражает к.т.н. Хайлову И.К., Сызько Э.В., д.ф.м.н. Подиивалову Д.Б.,

д.т.н. Перекатову В.И., Козлову Л.А., д.ф.м.н. Оленину А.С., к.т.н. Никольской Ю.Н., к.ф.м.н. Тарасенко Л.Г., д.т.н. Федорову В.Б., д.т.н. Торчигину В.П., д.ф.м.н. Захарову С.М., к.т.н. Шабанову Б.М., к.ф.м.н. Степанову А.М., к.т.н. Березко А.М., к.ф.м.н. Фетисову Н.С., к.ф.м.н. Копейкину А.Б., к.т.н. Кострюкову В.А., к.ф.м.н. Игнатову В.В., к.т.н. Гуснину С.Н., Андрееву А.В., Ткачеву В.А., Твердохлебову М.Н. и многим другим.

Автор чрезвычайно признателен Никитину Ю.В., Давыдовой Г.Н., Суима Е.А., Зотовой И.С., Табаковой Л.Н., Костеревой И.Н., Николаевой В.А., Шашуриной Т.П., которые в рекордно короткий срок подготовили сборник к печати.

Автор будет благодарен за мнения, высказанные об этой книге. Если читатели сочтут ее интересной, будет сделана попытка подготовить сборник по анализу архитектур более ранних разработок суперЭВМ советского периода.

В.С.Бурцев

# Значение создания ENIAC в развитии информационно-вычислительных и управляющих систем России

(Доклад на юбилейной сессии ЮНЕСКО по поводу пятидесятилетия создания первой ЭВМ ENIAC. Москва, 1996г.)

### В.С.Бурцев

### Аннотация

Отмечается, что создание первой ЭВМ дало мощный импульс в развитии информационной техники и изменило методы разработки сложных управляющих систем и объектов. Приводятся примеры из истории развития вычислительной техники в России, большинство из которых публикуются впервые.

Пятьдесят лет назад в университете Пенсильвании (США) был создан первый в мире электронный компьютер дискретного действия с автоматической обработкой информации в соответствии с заложенной в него программой. Значение этого события трудно переоценить, так как в результате был дан колоссальный импульс развитию такого свойства современного общества, как его информатизация. Это событие повлекло за собой коренной пересмотр методов научных исследований и разработок, в результате чего стало возможным создание новых сложных комплексов, определяющих научно-технический уровень развития общества. К числу достижений в этой области можно отнести: создание новых воздушных и морских лайнеров; бурное развитие атомной энергетики и освоение космоса; создание сложных радиолокационных и управляющих систем и многие другие направления прогресса. По ряду сложившихся обстоятельств этот импульс научно-технического развития особенно ощутим был в Советском Союзе - все основные передовые разработки и проекты уже с 1956 года базировались на использовании дискретной вычислительной техники, что не могло не стимулировать ее быстрое развитие. Процесс развития вычислительной техники лучше всего можно проследить по работам специалистов школы академика С.А.Лебедева, основоположника и

первопроходца вычислительной техники в Советском Союзе. Работы, проводимые школой С.А.Лебедева, не могли быть опубликованы до настоящего времени, так как основные и наиболее интересные из них выполнялись по заказам оборонных ведомств и были связаны с системами противоракетной и противосамолетной обороны, освоением космоса, созданием ядерных вооружений. После выхода целого ряда книг и статей по этим направлениям науки и техники [1,6,7,8] стало возможным проследить развитие вычислительной техники в нашей стране. Настоящее сообщение делает попытку в какой-то мере заполнить определенный пробел в истории развития отечественной вычислительной техники.

Первая электронная вычислительная машина дискретного действия, получившая название Малая электронная счетная машина (МЭСМ), была создана под руководством С.А. Лебедева в 1950 году в Институте электротехники АН Украины. машине С.А.Лебедев проверил многие принципы организации вычислительного процесса при работе в двоичной системе исчисления. Данная работа послужила хорошим экспериментом, позволившим ему уже через три года создать Быстродействующую электронную счетную машину (БЭСМ) для расчета многих задач экспериментальной физики и ряда других задач, которые ранее из-за большой трудоемкости счета решить было невозможно. Если МЭСМ производительность 50 оп/с, последовательное 17-разрядное арифметическое устройство (АУ) с фиксированной запятой, всего четыре арифметические операции и одну команду управления при емкости оперативного запоминающего устройства (ОЗУ) в тридцать одно слово, то БЭСМ в 1953 году обладала производительностью в 12 тысяч оп/с, имела параллельное 39-разрядное АУ с плавающей запятой, емкость ОЗУ 1024 слова и выполняла 32 различные операции. БЭСМ имела достаточно развитую систему внешней памяти: барабан, ленту, устройства ввода с перфокарт и устройство вывода на печатающее устройство. В БЭСМ существовали специальные команды изменения центрального и местного управления командами ИЦУК и ИМУК, обеспечивающие переход к подпрограммам с возвратом в исходную точку программы. В то же время управление БЭСМ было построено по последовательной схеме организации работы всех основных устройств - АУ, УК (управление командами), ОЗУ, барабана, ленты, печати и перфокарт.

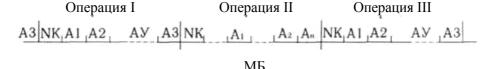

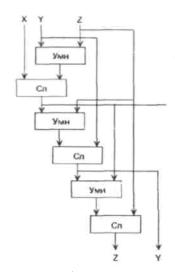

Рис.1. Временная работа БЭСМ.

NK - время обращения за командой, A1, A2 - время приема двух операндов, AV - время работы арифметического устройства, A3 - время записи результата, ME - время обращения к магнитному барабану,  $A_1$ , ...  $A_n$  - время обращения к памяти по записи или считыванию (пслов).

Согласно жесткой последовательности работы устройств БЭСМ (Рис. 1), сначала из ОЗУ считывался код команды, которая организовывала необходимые обращения к ОЗУ за считыванием первого и второго числа, выдавала необходимую

временную диаграмму для выполнения операции на АУ, записывала результат и считывала следующую команду. При обращении к ленте, барабану или внешним устройствам, центральное управление обеспечивало все операции поиска информации, ее считывания или записи, для чего использовалось АУ.

В 1953-1956 годах в Институте точной механики и вычислительной техники (ИТМ и ВТ) АН СССР проводились работы по автоматическому съему данных и сопровождению целей с радиолокационной станции (РЛС), которые открыли путь к созданию радиолокационных и ракетных комплексов на новой информационновычислительной основе. В 1955 году на макете радиолокационной станции обзорного действия был проведен эксперимент одновременного сопровождения нескольких реальных целей (самолетов) при опережающем расчете их траектории. Выдача координат осуществлялась в дискретном цифровом виде. В 1956 году этот эксперимент был повторен на серийной станции П-30 с посылкой оцифрованного сигнала управления на самолет перехвата целей. Работы проводились с использованием специальных ЭВМ "Диана I" и "Диана II". Оцифровку и селекцию данных, построение траекторий целей для их сопровождения осуществляла "Диана І", а решение задачи перехвата и выдачу команд управления "Диана ІІ". Эти работы позволили в 1960 году построить радиолокационный комплекс наведения противоракеты на баллистическую ракету противника с целью ее уничтожения осколочным зарядом с диапазоном отклонения от цели не более 25 метров. Для создать решения этой проблемы потребовалось высокопроизводительную вычислительную сеть. Производительность центральной ЭВМ этой сети достигала 40 тысяч оп/с при объеме ОЗУ в 4096 40-разрядных слов. Создание этой машины под названием  $\hat{M}$ -40 было закончено в 1958 году. Для достижения столь высокой производительности были существенно пересмотрены принципы организации системы управления ЭВМ.

Каждое устройство машины УК, АУ, ОЗУ, УВУ (управление внешними устройствами) получили автономное управление, что позволило реализовать их параллельную во времени работу. С этой целью был создан мультиплексный канал обращения к ОЗУ со стороны УК, АУ и УВУ.

| A1 A2 | ALU     | A3             |

|-------|---------|----------------|

| NK    | A1 A2   | ALU A3         |

|       | <u></u> | NK, AI A2, ALU |

|       |         | <u>NK</u>      |

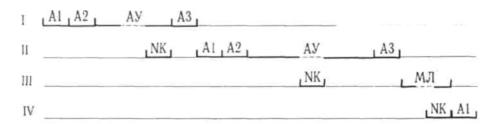

Рис.2. Временная диаграмма работы М-40.

<sup>/ -</sup> V - временные диаграммы выполнения арифметических операций, VI - временная диаграмма выполнения операций обращения  $\kappa$  внешним устройствам,  $A_1$ ,  $A_2$  - времена обращений  $\kappa$  O3V за операндом,  $A_3$  - время записи результата, NK - время считывания команды, AV - время работы AV.

Эти устройства рассматривались как самостоятельно работающие процессоры, обращающиеся к общему ОЗУ, то есть как машина, фактически представлявшая собой многопроцессорный комплекс.

Согласно временной диаграмме M-40 (Puc.2), обращение к памяти УК (A, A2, A3 и NK) и работы управления внешних устройств (УВУ), включая систему передачи данных, процессор ввода-вывода данных (ПВВ), происходят, как правило, на фоне работы АУ, УК, УВУ и ПВВ.

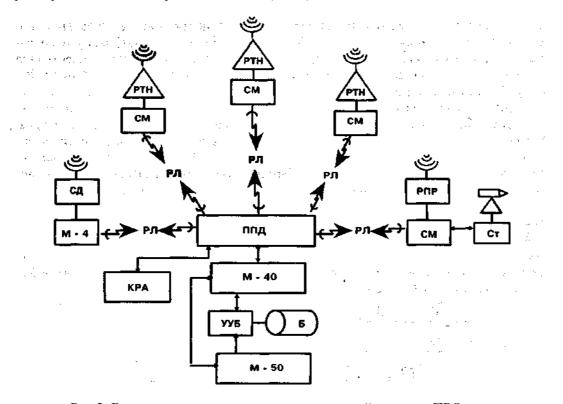

В экспериментальном комплексе противоракетной обороны (ПРО) эта машина осуществляла обмен информацией по пяти дуплексным одновременно и асинхронно работающим радиорелейным каналам связи с объектами, находящимися от нее на расстоянии от 100 до 200 километров; общий темп поступления информации через радиорелейные линии превышал 1 МГц (Рис.3).

Рис.3. Вычислительная сеть экспериментальной системы ПРО.

PTH - радиолокаторы точного наведения, CM - специальные вычислительные машины,  $C\mathcal{A}$  - станция дальнего обнаружения, M-4 - электронная вычислительная машина M-4,  $P\Pi P$  - радиолокатор противоракеты (передача сигналов управления на противоракету), CT - стартовая установка противоракет,  $\Pi\Pi\mathcal{A}$  - процессор приема и передачи данных, M-40 и M-50 - универсальные электронные вычислительные машины M-40 и M-50, E - запоминающее устройство на магнитном барабане, VVE - устройство управления барабаном, KPA - контрольно-регистрирующая аппаратура,  $P\Pi$  - радиорелейные линии.

Проблема обмена информацией с асинхронно работающими объектами была решена с помощью процессора ввода-вывода (ПВВ), работа которого основывалась

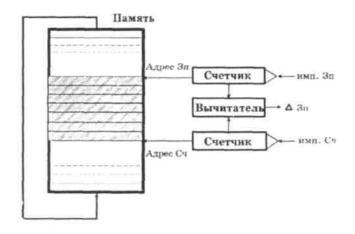

на принципе мощного мультиплексного канала, имеющего свою память, доступную для всех каналов.

Одновременно с проведением боевой работы М-40 осуществляла запись на внешнее запоминающее устройство (барабан) экспресс-информации, которая обрабатывалась на аналогичной ЭВМ М-50 (модернизация М-40, обеспечивающая работу с плавающей запятой). Боевые пуски по всем направлениям входа и выхода сопровождались записью информации на магнитные ленты контрольно-регистрирующей аппаратуры (КРА). Это давало возможность в реальном масштабе времени "проигрывать" и анализировать каждый пуск, для чего ЭВМ М-40 и М-50 имели развитую систему прерываний. Быстрому вводу вычислительной сети противоракетной обороны (ПРО) в значительной степени помог задел, который был создан в институте при разработке ЭВМ М-20. Проектирование этой ЭВМ было начато в 1955 году и завершено в 1958 году. Машина имела 20 тысяч оп/с, ОЗУ емкостью 4096 45-разрядных слов, арифметическое устройство с плавающей запятой, развитую систему внешних устройств, печатающее устройство с автономным управлением. На фоне работы арифметического устройства осуществлялась выборка следующей команды. Обеспечивалось автономное управление вводом-выводом (работа с печатью и перфокартами с использованием автономной памяти). Было сохранено централизованное последовательное управление АУ, ОЗУ и УК, за счет чего достигнута экономия оборудования при определенном проигрыше в скорости вычислений (Рис.4).

Рис.4. Временная диаграмма работы М-20.

$I_{\rm c}/I_{\rm c}/I_{$

ЭВМ М-20 хорошо зарекомендовала себя в эксплуатации и более десяти лет была основной ЭВМ общего назначения в СССР. М-20 была модернизирована (выполнена на полупроводниковой элементной базе), после чего она серийно выпускалась под названием БЭСМ-4.

Опыт эксплуатации экспериментального комплекса ПРО показал, что его вычислительные средства можно рассматривать как мозг всей системы; малейшие отклонения от нормы их функционирования приводят к нарушению работы всего комплекса, что может вызывать опасные ситуации. Поэтому при создании вычислительных средств на полупроводниковых элементах для боевого комплекса особое внимание было уделено устойчивости их работы при сбоях и отказах.

Рис.5. Вычислительная сеть ПРО. *ММК* - *многомашинный комплекс*.

Вычислительная сеть системы ПРО (Рис.5) имела протяженность несколько сот километров. Она состояла из вычислительных комплексов, каждый из которых был построен из идентичных боевых ЭВМ, обладающих полным пооперационным аппаратным контролем. Резервирование в комплексе обеспечивалось на уровне машин.

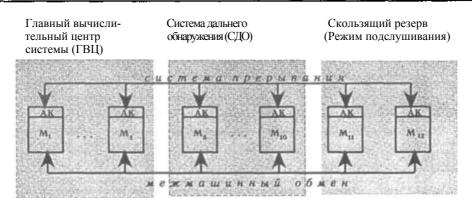

На Рис.6 показана структурная схема центрального 12 машинного комплекса системы ПРО со скользящим резервированием. На десять функционально работающих машин (M1 - M10) предусматривалось две машины (M11- M12) для горячего резервирования, которые работали в режиме "подслушивания" и были готовы в течение нескольких десятков миллисекунд заменить любую из вышедших из строя ЭВМ. Сигнал неисправности ЭВМ вырабатывался аппаратно системой пооперационного контроля каждой ЭВМ и посылался в систему прерывания всех машин. По межмашинному обмену наряду с данными боевого цикла передавалась необходимая экспресс-информация для ЭВМ, находящейся в резерве. В этом комплексе шесть ЭВМ ( $M_1$  -  $M_6$ ) решали задачу обнаружения целей по данным радиолокатора дальнего действия и построения их траекторий. Четыре ЭВМ ( $M_7$  -  $M_{10}$ ) решали задачи управления системой, включая распределение целей по стрельбовым комплексам.

Рис.6. Система сквозного резервирования на уровне машин.  $M_1$  -  $M_{12}$  - универсальные ЭВМ 5Э926, AK - система аппаратного контроля.

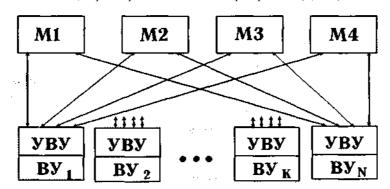

Эти ЭВМ, под названием 59526, имели производительность 0,5 млн. оп/с над числами с фиксированной запятой и ОЗУ объемом 32 тысячи 48 разрядных слов. Все основные устройства ЭВМ имели автономное управление, а управление внешними устройствами осуществлялось процессором передачи данных, имеющим довольно развитую специализированную систему команд. Серийный выпуск этих машин для управления различными стационарными средствами вооружения был начат с 1966 года. Машина была модернизирована в части введения арифметики с плавающей запятой и мультипрограммного режима. Модернизированная ЭВМ имела название 5Э51 и серийно выпускалась с 1967 года для построения мощных вычислительно-информационных центров повышенной надежности. Благодаря автономной работе ее основных устройств и, в первую очередь, процессора ввода-вывода, на базе общего ОЗУ эти машины успешно использовались при создании многомашинных комплексов с единой внешней памятью, состоящей из большого количества барабанов, дисков и лент. Структурная схема одного из таких комплексов, Центра контроля космического пространства (ЦККП), показана на Рис.7.

Центр контроля космического пространства (ЦККП)

Рис.7. Многомашинная работа на единую внешнюю память. M1 - M4 - 3BM 5351, VBV - устройства управления внешней памятью и устройствами ввода-вывода, BV - внешние устройства (внешняя память, управление каналами обмена и устройствами ввода-вывода).

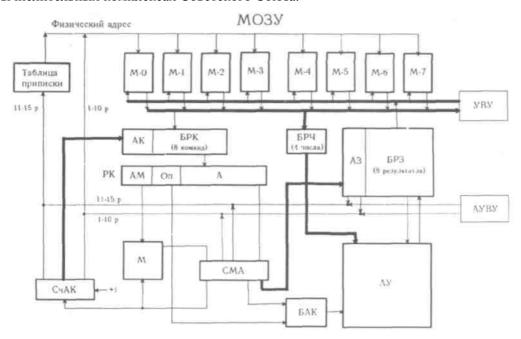

В это же время, в институте на аналогичной полупроводниковой элементной базе создается универсальная ЭВМ БЭСМ-6 (Рис.8), которая в течение двадцати лет широко использовалась как основная быстродействующая ЭВМ в различных вычислительных комплексах Советского Союза.

Рис. 8. Блок-схема центральной части машины БЭСМ-6.

A - адрес оператора, A3 - буфер адресов записи, AK - буфер адреса команд, AM - адрес модификатора, AVBV - адрес устройства управления внешними устройствами, EAK - базовый адрес команды, EAK - буферные регистры команд, EAK - буферные регистры записи результата, EAK - буферные регистры чисел, EAK - EAK

оригинальной схемотехники и конструкции БЭСМ-6 имела производительность 1млн. оп/с, объем ОЗУ 32 тысячи 50-разрядных слов, АУ параллельного типа с плавающей запятой. Существенного увеличения производительности БЭСМ-6 удалось достичь за счет использования конвейерного принципа организации вычислительного процесса и введения интерливинга в модульную память (интерливинг на 8 модулей). Для записи чисел были использованы регистры с ассоциативной выборкой (типа кэш). Эффективная работа с математической памятью обеспечивалась при аппаратной поддержке защиты в многопрограммном режиме работ. С этой же целью был введен специальный привилегированный режим работы для отдельных блоков операционной системы. В сохранился централизованный принцип управления устройствами, что существенно сдерживало организацию параллельной работы внешних устройств и затрудняло создание комплексов с общей внешней памятью и работу с каналами связи. Чтобы обеспечить комплексирование БЭСМ-6, на той же элементно-конструктивной основе был разработан комплекс

АС-6, позволявший объединять ОЗУ нескольких машин в общую память высокопроизводительными каналами с пропускной способностью в 1,3 млн. слов в секунду каждый. В комплексе предусматривался второй уровень коммутации внешних устройств и каналов связи, для чего использовались автономные системы управления каналами связи и внешними устройствами; эти системы сопрягались со стандартным каналом связи внешних устройств производительностью 1,5 Мб/с. Управление комплексом осуществлялось новым процессором АС-6 с отличной от БЭСМ-6 системой команд. Система АС-6 была реализована в трех взаимно дублирующих вычислительных центрах обработки космической информации.

Таким образом, С.А.Лебедев как главный конструктор всех разработок умело использовал финансовые и приоритетные возможности военных заказов, разрабатывая параллельно более дешевые высокопроизводительные ЭВМ гражданского применения.

Так, в связи с необходимостью дальнейшего развития высокопроизводительных ЭВМ, уже в 1967 году встал вопрос о переходе на новую конструктивнотехнологическую базу с использованием интегральных схем (ИС) и печатных плат. Это требовало переоснащения Института и работающих с ним заводов, освоения новых методов автоматизированного проектирования для размещения ИС, трассировки многослойных печатных схем и межблочного монтажа, создания тестоводиагностических программ.

Такое переоснащение можно было осуществить, только взяв заказ на разработку серийной возимой вычислительной системы для противосамолетного комплекса С-300. По этой разработке ИТМ и ВТ впервые был заказчиком серии интегральных схем (ТТЛ) для цифровой техники в Министерстве электронной промышленности и получил достаточно средств на переоснащение заводов и Института. Так как комплекс требовал повышенной устойчивости при работе в сложных климатических и вибрационных условиях, он был реализован по крупномодульному принципу с полным автономным аппаратным контролем каждого модуля. Резервирование комплекса осуществлялось не на машинном уровне, а на уровне модулей основных устройств ЭВМ, что значительно эффективнее.

ЭВМ 5Э26 (Рис.9) имела суммарную производительность трех процессоров 1 млн. оп/с, арифметико-логическое устройство (АЛУ) с фиксированной запятой с шириной слова в 35 разрядов, ОЗУ емкостью 32 Кбит. В дополнение к ОЗУ имелась память команд (ПК) объемом 64 Кбит. ПК была реализована на бибсах (ферритовых сердечниках с двумя взаимно перпендикулярными отверстиями), работала без разрушения считываемой команды и обеспечивала хранение информации без расхода энергии. Общий объем ЭВМ составлял менее 2,5 м³, а потребляемая мощность имела значение порядка 5 кВт. Реализация вычислительного комплекса с такими параметрами стала возможной только при использовании ИС и конструкции на многослойных печатных платах. Комплекс 5Э26, несмотря на достаточно низкую надежность ИС на первом этапе их производства ( $\lambda > 10^{-6}$ ), обеспечивал функциональную надежность не ниже 0,99 в самых тяжелых условиях большого перепада температур, повышенной влажности и тряски при резервировании АУ и УК два из трех и стопроцентном резервировании ПК, ОЗУ и УВУ.

Рис.9. Система резервирования на уровне модулей устройств возимой ЭВМ 5Э26 AV-арифметическое устройство, УУ - устройство управления, АК - пооперационный аппаратный контроль, КМ - разнесенный (по модулям) центральный коммутатор, ПК - неразрушаемая память команд, УВУ - устройство управления внешними устройствами, ОЗУ - оперативное запоминающее устройство.

При этом удалось реализовать такую скорость замены дефектных устройств, что практически на всей временной диаграмме функционирования комплекса сбои и отказы устройств не влияли на нормальное продолжение его боевой работы.

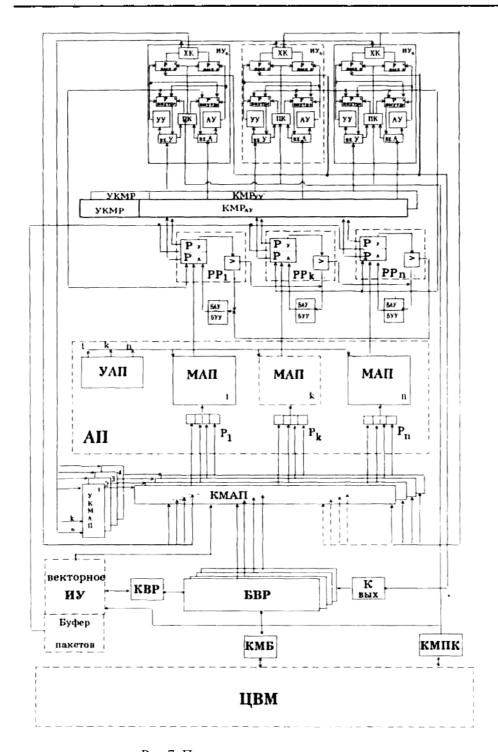

Естественным продолжением работ по многопроцессорной архитектуре ЭВМ было создание на этом принципе комплекса вычислительных средств, обладавшего предельной производительностью при частотных характеристиках элементов, которые обеспечивала технология того времени. В отличие от машины 5Э26, где многопроцессорный модульный принцип был использован, в основном, для обеспечения высоких надежностных характеристик, он, наряду с высокими показателями надежности в многопроцессорном вычислительном комплексе МВК "Эльбрус-2", обеспечил предельную производительность. Производительность многопроцессорной системы, в основном, ограничивается двумя факторами: пропускной способностью коммутатора между процессорами и ОЗУ и сложностью организации корректной работы сверхоперативной кэш памяти. Трудности, возникающие при решении этих двух проблем, существенно увеличиваются с ростом количества процессоров. Пропускная способность коммутатора "Эльбрус-2" достигала 2Гбайт/с. Корректность работы сверхоперативной памяти была обеспечена путем ее разбиения на несколько частей, каждая из которых имела свой алгоритм работы в соответствии с выполняемой функцией. Так, в МВК "Эльбрус-2" имеется: сверхоперативная память команд, массивов, локальных данных, безадресный буфер быстрых регистров, построенный по принципу потока данных и буфер глобальных данных. Корректность работы буфера глобальных данных с ОЗУ вызывает те же проблемы в многопроцессорном комплексе, которые возникают в сверхоперативной КЭШ. В МВК "Эльбрус-2" реализована схема корректности работы этого буфера, которая обеспечивает корректную работу комплекса, практически не замедляя ее вне зависимости от числа процессоров [4]. Аналогичные схемы, используемые в современных комплексах фирмы Hewlett Packard (SPP-2000) и Silicon Graphics, существенно уступают по эффективности схеме МВК "Эльбрус-2". МВК "Эльбрус-2" создавался в два этапа:

- на первом этапе отрабатывались новые архитектурные принципы, включая программное обеспечение;

Общее количество устройств - 1016

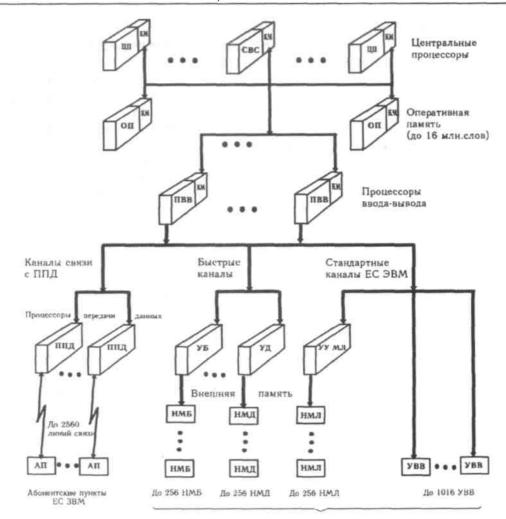

### Рис.10. Структура МВК "Эльбрус".

ЦП - центральный процессор, ОП - оперативная память, КМ - коммутатор, обеспечивающий доступ каждого ЦП к каждому модулю ОП и ПВВ, ПВВ - процессор вводавывода, ППД - процессор передачи данных, УБ - устройство управления барабанами, УД - устройство управления дисками, УУ МЛ - устройство управления магнитными лентами, НМБ - накопитель на магнитных барабанах, НМД - накопитель на магнитной ленте, УВВ - устройства ввода-вывода.

- на втором этапе наряду с принципами архитектуры отрабатывалась новая конструкторско-технологическая база.

На первом этапе был реализован 10-процессорный комплекс "Эльбрус-1" производительностью в 15 млн. оп/с на элементно-конструкторской базе 5Э26 на ТТЛ элементах с задержкой 10-20 нс на вентиль. На втором этапе был создан МВК "Эльбрус-2", производительностью 120 млн. оп/с и с объемом ОЗУ 160 Мбайт, построенный на элементной базе типа Motorola 10000 с задержкой 2-3 нс на вентиль.

,

МВК "Эльбрус" (Рис.10) построен по модульному принципу и в зависимости от комплектации может включать необходимое количество центральных процессоров (1-10), модулей оперативной памяти (4-32), процессоров ввода-вывода (ПВВ) (1-4), устройств внешней памяти (барабанов, дисков, магнитных лент), процессоров передачи данных (ППД) (1-16) и устройств ввода-вывода, подключенных либо непосредственно к ПВВ, либо через линии передачи данных посредством ППД. Каждый компонент комплекса, включая разнесенные по ним узлы центрального коммутатора, имеет стопроцентный аппаратный контроль и при появлении хотя бы одиночной ошибки в ходе вычислительного процесса выдает сигнал неисправности. По этому сигналу операционная система через аппаратно реализованную систему реконфигурации исключает неисправный модуль из работы.

Отключенный модуль попадает в ремонтную конфигурацию, в которой посредством тест-диагностических программ и специальной аппаратуры ремонтируется, после чего может быть включен операционной системой в рабочую конфигурацию.

Описанная структура позволяет осуществить резервирование на уровне однотипных модульных устройств. Время подключения резервного модуля не превосходит 0,01 сек, что обеспечивает бессбойную работу комплекса с заданной надежностью для всех боевых систем.

К особенностям МВК "Эльбрус-2", кроме описанных выше, можно отнести следующие:

- система команд эффективно реализует автокод, являющийся языком высокого уровня;

- аппаратно поддержаны часто встречающиеся программные конструкции языков высокого уровня;

- осуществлена обезличенная работа однотипных модулей процессоров,  $\Pi B B$ ,  $\Pi \Pi \Pi$ :

- аппаратно реализована в ПВВ работа диспетчера внешних объектов;

- система команд и математическое обеспечение ППД позволяют достаточно просто адаптироваться к различным вычислительным сетям и внешним объектам;

- в качестве одного из процессоров может быть подключен любой спецпроцессор (если таким спецпроцессором является процессор, то достигается производительность, более чем в шесть превышающая производительность БЭСМ-6).

Аванпроект МВК "Эльбрус" был выполнен в 1970 году, МВК "Эльбрус-1" сдан Госкомиссии в 1980 году, а МВК "Эльбрус-2" в 1985 году. Оба комплекса серийно выпускались более 15 лет.

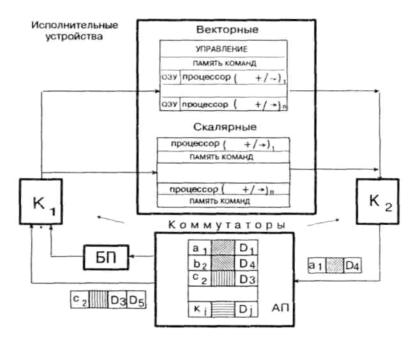

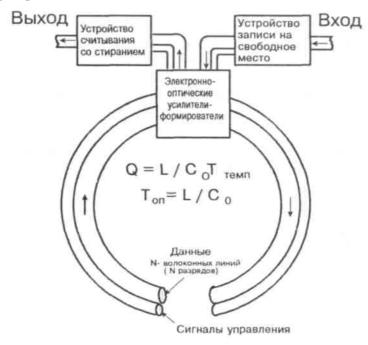

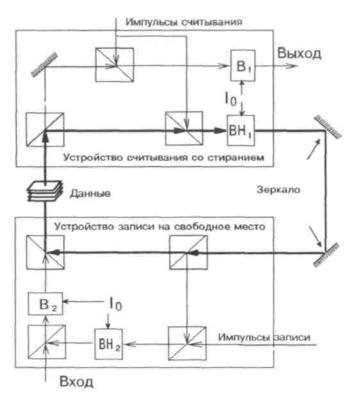

За последние 10 лет в России специалистами школы академика С.А.Лебедева было разработано много интересных проектов, внесших существенный вклад в развитие архитектуры суперкомпьютеров, однако по тем или иным причинам они не были реализованы в серийном производстве. К ним надо отнести: векторный процессор МВК "Эльбрус-2", модульный конвейерный процессор, МКП ССБИС, оптическую сверхвысокопроизводительную вычислительную машину (ОСВМ) РАН и ряд других.

В заключение можно сказать, что по целому ряду архитектурных и схемотехнических решений российская школа суперЭВМ нисколько не отстает от

зарубежной. Поэтому научно-техническое сотрудничество с зарубежными коллегами в области создания суперЭВМ было бы чрезвычайно полезным для обеих сторон.

### Литература

- 1. Б.Н.Малиновский. История вычислительной техники в лицах.

- 2. Вычислительные машины с нетрадиционной архитектурой. Супер-ВМ. Сборник научных трудов ВЦКП. вып.2. Москва 1994.

- 3. Академия наук УССР. Библиография ученых Украинской ССР. Сергей Алексеевич Лебедев. Киев, Наукова Думка 1978.

- 4. В.С.Бурцев Принципы построения многопроцессорных вычислительных комплексов "Эльбрус". Доклад на научно-техническом семинаре Многопроцессорные вычислительные комплексы. Москва 21-22 ноября 1977. Препринт № 1 за 1977.

- 5. Л.Н.Королев, В.А.Мельников. Об ЭВМ БЭСМ-6. Управляющие системы и машины, 1976, 6.

- 6. Голубев О.В., Каменский Ю.А., Минасян М.Т., Пупков Б.Д. Российская система противоракетной обороны (прошлое и настоящее взгляд изнутри). Техноконсалт, Москва, 1994.

- 7. Кисунько Г.В. Секретная зона. Москва, Современник, 1996.

- 8. Бакулев П.А., Сотский Н.М., Горохов Ю.И. О некоторых работах в СССР по внедрению средств цифровой автоматики в радиолокацию и в радиотехнические комплексы управления летательным аппаратом.

- 9. Бурцев В.С. Новые подходы к оценке качества вычислительных средств. (в данной книге)

### О необходимости создания суперЭВМ в России

Бурцев В.С.

#### Аннотация

В статье приведены требования, предъявляемые к суперЭВМ при решении сложных задач. Дана оценка возможностей современных суперЭВМ. Указаны основные причины, сдерживающие достижение требуемой производительности. Указано на особые условия развития суперЭВМ в нашей стране. Сделан вывод о необходимости создания суперЭВМ в России на зарубежной элементной базе.

В последнее время, очевидно, под воздействием быстро развивающихся технологических возможностей, которые привели созданию К однокристальных микропроцессоров (Альфа, Power PC, Pentium, Intel 860 и др.), все чаще высказывается мнение, что время суперЭВМ уже прошло, что все задачи можно решить на современных РС и рабочих станциях, объединенных в единую локальную сеть. Самое странное, что такие мнения высказываются в академических кругах и в газете "Поиск". Некоторые ученые в своих высказываниях идут даже дальше и говорят о том, что больших задач, для которых необходимы суперЭВМ, в академии нет. Они пытаются объяснить этот "феномен" тем, что математические методы решения сложных задач, разработанные нашими математиками, позволили решать эти сложные задачи на рабочих станциях.

Все это заставило меня написать эту статью и попытаться ответить на следующие вопросы:

- каковы современные требования, предъявляемые к суперЭВМ, исходя из необходимости решения проблемных задач первостепенной важности;

- каковы возможности современных РС, рабочих станций и суперЭВМ в настоящее время;

- можем ли мы создать суперЭВМ, соответствующую современному мировому уровню или даже превышающую по характеристикам зарубежные, и надо ли этим заниматься.

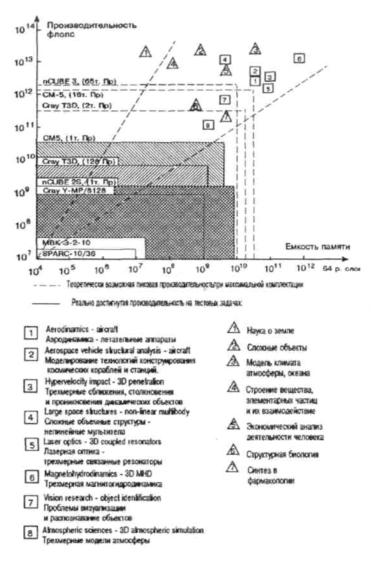

Для определения основных требований, предъявляемых к суперЭВМ сложными проблемными задачами, воспользуемся данными, приведенными американским ученым Гарри Джонсоном из суперкомпьютерного центра в Северной Каролине, США [1], и мнением наших ведущих ученых, работающих в различных направлениях исследований и широко использующих математические методы моделирования. На Рис.1 в координатах производительность-память даны требования к суперЭВМ для различных задач. Производительность посчитана исходя из требования 15-минутного решения задачи. Американские данные помечены квадратами. Требования к аналогичным задачам, которые привели наши математики, того же порядка (они обозначены треугольниками) Пунктирной линией показана область, которую перекрывают наиболее производительные суперЭВМ по теоретической пиковой производительности - это Cray T3D, nCUBE-3 и CM-5, ориентированные на решение задач уравнений математической физики.

Машины с такой пиковой производительностью (максимальной комплектации) еще не созданы, поэтому сплошной чертой показана производительность реально работающих машин, полученная на фрагментах тестовой задачи [2]. На этом же графике показана область, которую перекрывают универсальные, наиболее производительные многопроцессорные суперЭВМ конвейерного типа Сгау Y-MP. Из приведенной на Рис.1 информации можно сделать вывод, что суперЭВМ в настоящее время не удовлетворяют предъявляемым к ним требованиям по производительности и объему памяти на несколько порядков. Однако, не стоит делать неправильного вывода о том, что задачи по этим направлениям в настоящее время не решаются. Анализ данных, приведенных в [1], показывает, что по всем из обозначенных на рисунке направлениям ведутся работы на существующих суперЭВМ, однако выполняемые ими задачи не решают поставленных проблем в полном объеме. Решаемые задачи развиваются в соответствии с развитием возможностей суперЭВМ. По каждому направлению вырабатывается своя линия развития задачи, которая во многом определяется возможностями суперЭВМ на каждый момент времени.

На Рис.2 в качестве примера показаны три направления исследований, каждое их которых обозначено на рисунке соответствующим значком. Из рисунка видно, что вычислительные средства в настоящее время не удовлетворяют требованиям этих задач (незаштрихованные значки). В то же время многие задачи по направлениям этих исследований решаются на существующих суперЭВМ (заштрихованные значки).

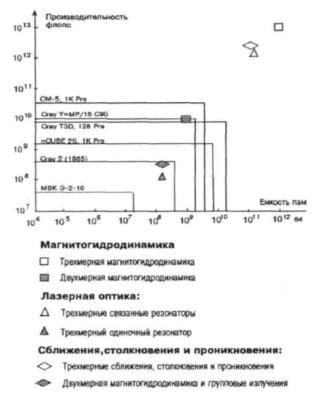

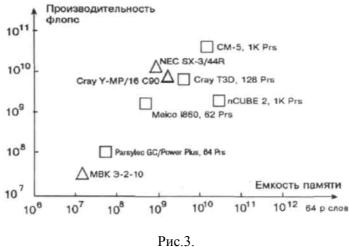

В той же плоскости координат на Рис.3 показаны возможности двух типов вычислительных систем:

- многопроцессорных комплексов с универсальными скалярно-векторными конвейеризованными процессорами; эти структуры (помеченные на рисунке треугольниками), где каждый процессор имеет прямой доступ к каждому модулю общей памяти, называют системами с распределяемой памятью в отличие от многопроцессорных систем с распределенной памятью;

- многопроцессорных систем с распределенной по процессорам памятью (Cray T3D, транспьютерные системы Парситек, nCUBE-2 и CM-3 (помечены квадратами); в некоторых работах их относят к многомашинным комплексам [3].

Рис.1

Как уже отмечалось, даже самые лучшие суперЭВМ настоящего времени по производительности на несколько порядков не отвечают требованиям больших задач.

Каковы те принципиальные причины, которые не позволяют построить суперЭВМ требуемой производительности? Если совсем коротко, то они ограничены отводом тепла от полупроводниковых схем. Принципиально жидкостное охлаждение позволяет отвести 20 Вт с одного квадратного сантиметра. Следовательно,

чем меньше выделяет энергии схема на одно логическое срабатывание Аэ, тем меньше выделяется мощности Рэ=Аэ/tэ при том же быстродействии, где tэ - время срабатывания элемента. Следовательно, в одном и том же объеме можно сосредоточить большее количество логических элементов и элементов памяти. Если объем растет, растут потери во времени на связи между элементами tсв и времена tэ становятся соизмеримы, а иногда и много меньше, чем tсв. Поэтому, чем выше производительность элемента, тем меньший объем должна иметь вычислительная система.

Рис.2

Отсюда можно сделать два вывода:

- суперЭВМ должна иметь эффективную и достаточно мощную жидкостную систему охлаждения;

- предельное быстродействие во многом зависит от качества логического элемента, его времени срабатывания to и выделяемой при этом энергии.

Безусловно, немалую роль при создании супер ЭВМ играет показатель надежности элемента X. На практике зарубежных разработок этот параметр не ограничивает производительности, т.к. даже для схем большой интеграции величина  $\lambda$  не превышает  $10^{-8}$ . Наша элементная база, в особенности на первом этапе производства, имеет  $\lambda > 10^{-6}$ , что заставляет вводить резервирование и

аппаратный контроль во все устройства машины, а последнее увеличивает объем устройств и потребляемую ими мощность.

Анализ показывает, что предельная производительность одного процессора, работающего по фон-Неймановскому принципу, вряд ли превзойдет 10<sup>8</sup> oп/с на скалярных операциях [4]. Практика и анализ задач позволяет сделать вывод, что в одном процессоре конвейерного типа производительность на векторных операциях может быть поднята не более, чем на один порядок [5]. Увеличить производительность до  $10^{14}$  оп/c, т.е. еще на пять порядков, можно только путем распараллеливания вычислительных процессов. Первым шагом в этом направлении являются многопроцессорные комплексы, как правило, состоящие из 4-16 процессоров, работающих на одну общую память.

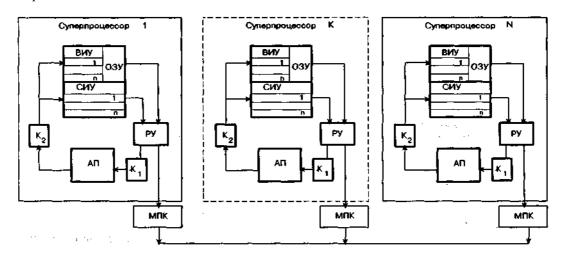

Дальнейшее распараллеливание вычислительных процессов приводит к системам с массовым параллелизмом. Системы массового параллелизма насчитывают сотни, а иногда и тысячи параллельно работающих процессоров и строятся, как правило, на базе систем с распределенной по процессорам памятью.

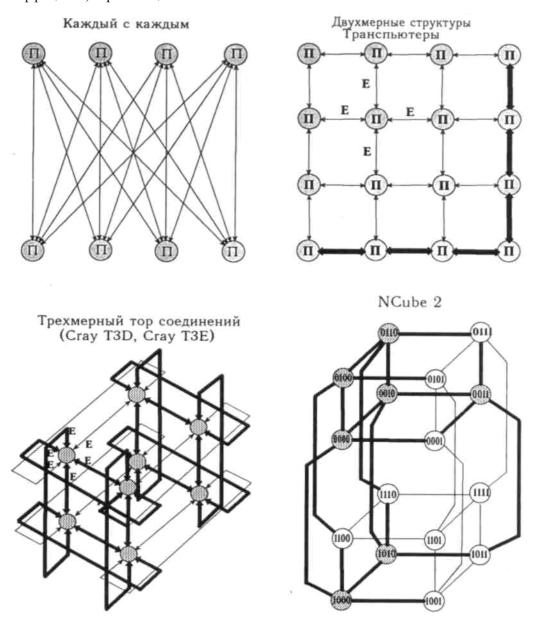

Основное различие всех параллельных вычислительных систем сводится к способам коммутации процессоров. Так, многопроцессорные системы распределяемой общей памятью имеют центральный коммутатор большой пропускной способности, обеспечивающий доступ каждого процессора к каждому модулю ОЗУ. Такие комплексы с небольшим количеством процессоров (1-16) можно считать достаточно универсальными. Увеличение процессоров в этой системе увеличивает время обращения к ОЗУ, что резко снижает быстродействие каждого процессора.

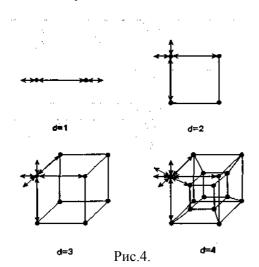

Системы с распределенной по процессорам памятью, как правило, имеют многоступенчатую систему коммутации.

Транспьютерная система коммутации, например, характерна тем, что каждый микропроцессор имеет четыре связи с соседними процессорами, как правило,

последовательного типа. Эти системы в большей степени ориентированы на решение двумерных задач.

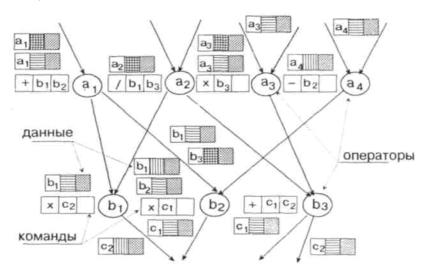

Вычислительный комплекс Cray T3D имеет в каждом узле системы связи по трем взаимно перпендикулярным направлениям, причем каждое направление связи замкнуто в кольцо. Эта система максимально ориентирована на решение трехмерных залач.

СуперЭВМ СМ 5 и пСИВЕ 2-3 имеют межпроцессорные связи типа гиперкуб, причем, чем количество процессоров N больше, тем больше ранг коммутации d (согласно формуле N=2<sup>d</sup>). Пользуясь таким представлением, можно коммутацию транспьютерных систем охарактеризовать как d=2, а коммутацию, принятую в T3D, как d=3 (Рис.4). Из рисунка видно, что передача данных между предельно отстоящими друг от друга процессорами в транспьютерной системе может быть осуществлена за шагов, в системе T3D за  $3/2\sqrt[3]{N}$  двойка в знаменателе появляется за счет замыкания ортогональных связей в кольцо), а в системе гиперкуба за d шагов. Все эти системы массового параллелизма являются в большей или меньшей степени специализированными системами, причем специализация их увеличивается с увеличением числа процессоров и степени ограничений, принятых в системе коммутации. Так, транспьютерная система массового параллелизма, имеющая большие ограничения связи между процессорами, специализированной, чем системы CM-5, nCUBE 2-3 и Cray T3D. В то же время, система Стау ТЗD, имеющая преимущества по решению трехмерных задач, является более специализированной системой, чем СМ-5 и nCUBE 2-3. Этим и можно объяснить то обстоятельство, что Сгау Т3D используется только совместно с Сгау Ү-МР или Стау С90.

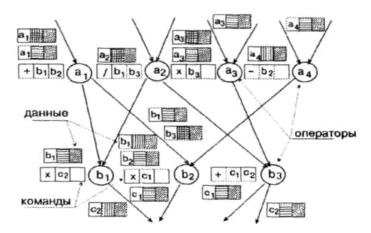

Что же мешает многопроцессорным системам **MPP** системам достичь предельной. наперед заданной производительности путем простого увеличения процессоров? Есть две основные причины, которые не позволяют это сделать в том случае, если вычислительный процесс традиционному реализуется ПО Неймановскому принципу:

- первое это большое время передачи данных между процессорами;

- второе невозможность в статике при написании программ или при их трансляции эффективно использовать ресурсы системы: процессоры, память, каналы передачи информации и др.

Второе относится и к многопроцессорным вычислительным системам, работающим с распределяемой общей памятью.

Таблица 1 иллюстрирует загрузку процессоров в таких системах, которая резко падает от увеличения числа процессоров, даже на тестовых задачах. Человек

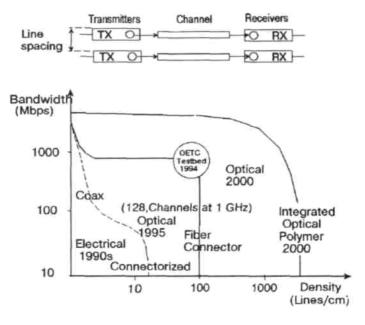

в статике не может загрузить такие системы, т.к. он не знает, сколько времени для того или иного вычислительного процесса будет занят процессор. Выход единственный - переход к распределению аппаратными средствами по свободным вычислительным ресурсам (процессорам, памяти, каналам передачи и др.), готовых к выполнению параллельных вычислительных процессов. Другими словами, достижение предельного параллелизма прохождения вычислительных процессов требует новых, нетрадиционных принципов их организации. Такие новые нетрадиционные вычислительные структуры МРР и у нас, и за рубежом успешно разрабатываются. Эти системы базируются на мощных системах коммутации, обладающих высоким темпом работы. Наверное, полупроводниковая вычислительная техника не сможет выдержать конкуренцию с оптоэлектронными коммутационными системами для новых вычислительных систем. Зарубежный анализ показывает (Рис.5), что в 1995-2000 г.г. оптоэлектронные коммутаторы вытеснят электронные [5].

| No of<br>Processors                                | System                        | Peak speed gigaflops | Benchmark                   | Efficiency<br>(code/peak) |  |  |

|----------------------------------------------------|-------------------------------|----------------------|-----------------------------|---------------------------|--|--|

| NAS Parallel Benchmark EP (size: 2 <sup>28</sup> ) |                               |                      |                             |                           |  |  |

| 16                                                 | Cray C90                      | 16                   | 8.3                         | 50%                       |  |  |

| 128                                                | Intel<br>iPSC/860             | 2.6                  | 0.4                         | 15%                       |  |  |

| 65536                                              | Thinking<br>Machines CM-<br>2 | 1620                 | 2.4                         | 12%                       |  |  |

|                                                    | NAS Parallel Bench            | hmark FFT (siz       | ze: 256 <sup>2</sup> x 128) |                           |  |  |

| 16                                                 | Cray C90                      | 16                   | 4.5                         | 30%                       |  |  |

| 128                                                | Intel<br>iPSC/860             | 2.6                  | 0.5                         | 20%                       |  |  |

| 65536                                              | Thinking Vfchines CM-2        | 14                   | 0.5                         | 4%                        |  |  |

|                                                    | NAS Parallel Be               | nchmark CG (s        | size 2 x 10 <sup>6</sup> )  |                           |  |  |

| 16                                                 | Cray C90                      | 16                   | 2.6                         | 16%                       |  |  |

| 128                                                | Intel<br>iPSC/860             | 2.6                  | 0.07                        | 3%                        |  |  |

| 16384                                              | Thinking Machines CM          | 35                   | 0.7                         | 3%                        |  |  |

Source; NASA Ames Research Center, Technical Report RNR-92 CC2 NAS = Numerical Aerodynamic Simulation

Таблица 1.

Итак, требуемая производительность  $10^{14}$  оп/с в начале 2000-х годов, очевидно, будет достигнута. Спрашивается, необходимо ли нам заниматься суперЭВМ и можем ли мы создать конкурентоспособную суперЭВМ или нам

следует пойти по пути европейских стран и покупать суперЭВМ за рубежом. Есть несколько веских причин, говорящих о том, что необходимо создавать свои суперЭВМ.

Первое: даже если не принимать во внимание то, что военные объекты особой важности базируются и разрабатываются на основе суперЭВМ, решение перечисленных на Рис.1 проблем имеет определяющее значение для развития страны. Та страна, которая первой будет иметь возможнось решать эти задачи, всегда будет иметь преимущество в научно-техническом потенциале. Поэтому ни одна страна наиболее быстродействующую систему не продаст - мы будем иметь в лучшем случае системы "second hand" и решаемые задачи будут под контролем конкурентов.

Рис. 5.

Второе: как показывает история становления вычислительных средств, суперЭВМ являются передовым фронтом развития всей вычислительной техники. Сохраняя разработки суперЭВМ, мы сохраняем передовые школы, определяющие развитие информатики в нашей стране.

Третье: в странах, где будут созданы самые высокопроизводительные вычислительные системы, будут и самые высокоинтеллектуальные талантливые научные кадры пользователей.

Четвертое: эксплуатация суперЭВМ, даже уровня "second hand", будет обходиться намного дороже, чем эксплуатация вычислительных средств собственной разработки.

Пятое: созданные в России суперЭВМ на современной зарубежной базе наверняка выиграют конкуренцию у зарубежных фирм как по архитектурным и схемотехническим решениям, включая системное матобеспечение, так и по

себестоимости. Эта наукоемкая продукция без сомнения найдет сбыт и позволит сохранить рентабельное производство вычислительной техники в целом.

Последнее заявление, безусловно, у многих вызовет по меньшей мере скепсис. Действительно, на вопрос: "Имели ли мы когда-нибудь суперЭВМ мирового уровня?" можно четко ответить: "Нет". В то время, когда мы заканчивали разработку, за рубежом всегда была суперЭВМ более быстродействующая, чем наша, построенная на элементной базе следующего поколения.

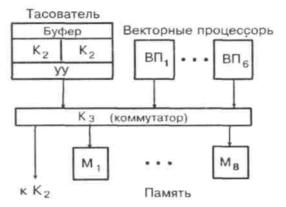

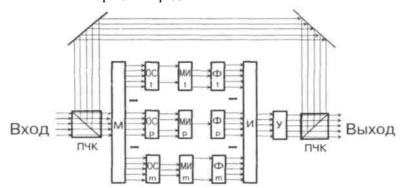

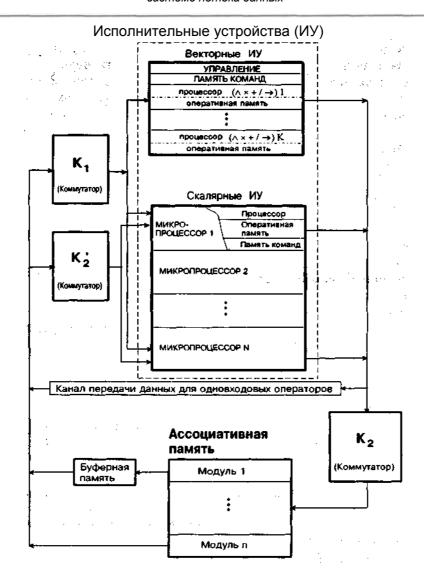

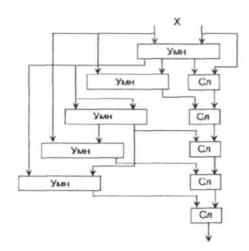

Но тем не менее, наши разработки по схемотехническим, архитектурным и конструктивным характеристикам зачастую превышали зарубежный уровень. Так, мы уже в 1970 году разработали идеологию многопроцессорной (10-процессорной) суперЭВМ, в то время как построения 4-процессорных комплексов в ІВМ кончались полной неудачей - резко падала общая производительность системы. Процессор МВК "Эльбрус-2" на элементах с задержкой  $\tau = 2$  нс имел ту же производительность, что и компьютер типа Cyber на элементах с задержкой τ =1 нс. Разработанный в 1978 году векторный процессор, входящий в состав МВК "Эльбрус-2", имел большую команду, систему "разгона" и "торможения" и другие оригинальные решения, за счет которых на элементной базе МВК "Эльбрус-2" он достиг производительности 80 мегафлоп (той же, что и компьютер Cray на элементной базе с  $\tau = 0.7$ ). Созданный в ИТМ и ВТ векторный процессор МКП имеет производительность порядка 200 мегафлоп на элементной базе с  $\tau = 1,2$  нс. Производительность достигается за счет оригинального схемотехнического решения - аппаратного распараллеливания скалярных и векторных операций. Векторный процессор ССБИС имел целый ряд оригинальных решений обработки данных на проходе и др. В настоящее время в РАН разработана и испытана на модели система массового параллелизма с автоматическим распределением ресурсов, имеющая целый ряд оригинальных решений. Система работает по новому не фон-Неймановскому принципу организации вычислительных процессов. Поэтому можно совершенно ответственно утверждать, что разработанная нашими специалистами суперЭВМ на современной элементной базе будет по многим параметрам превосходить зарубежные.

Безусловно, возникает вопрос, можно ли использовать зарубежную элементную базу и не станет ли она при определенных обстоятельствах камнем преткновения. Надо сказать, что в этом отношении суперЭВМ находится в лучшем положении, чем РС или рабочие станции. Последние изготавливаются и используются в больших количествах и обеспечение их зарубежной элементной базой довольно проблематично. В частности, если поставщик внесет изменения или сменит продукцию на новую, мы попадаем в полную зависимость от него.

С суперЭВМ дело обстоит гораздо проще. Как показывает зарубежный опыт (США), количество суперЭВМ в стране не превосходит двух десятков. Для России вполне достаточно иметь пять региональных вычислительных центров с развитой системой теледоступа, благодаря которой, как правило, почти каждый пользователь имеет доступ к суперЭВМ со своего рабочего места, и центры для исследовательских институтов различных направлений народного

хозяйства. На такое количество, и даже большее, можно закупить элементную базу на весь период эксплуатации.

Все это говорит о том, что в нашей стране необходимо создавать суперЭВМ как объект первостепенной важности. Это наукоемкое изделие требует в настоящее время разрешения целого ряда фундаментальных проблем, связанных с нетрадиционной организацией массовых параллельных вычислительных процессов. Многие из них нашли отражение в проекте ОСВМ РАН (посвященном созданию оптической сверхвысокопроизводительной машины), успешно защищенном в 1993 г.[6].

В заключение попытаемся определить, что же такое суперЭВМ и каковы ее основные характеристики, отличающие ее от других классов машин?

СуперЭВМ - это достаточно универсальные вычислительные средства, обладающие на данный момент времени максимальной производительностью.

Так, в 60-е годы к суперЭВМ относились машины производительностью более 1 млн. операций в секунду.

В 2000-х годах к суперЭВМ будут относится комплексы вычислительных средств производительностью выше  $10^{13-14}$  операций в секунду. Вычислительные комплексы такой производительности, как правило, будут использовать жидкостное охлаждение, широкополосную оптоволоконную систему теледоступа, терабайтные хранилища информации с автоматизированным доступом к ней и развитую систему визуализации информации и процессов.

Каждый региональный центр на базе одной или нескольких суперЭВМ будет по каналам теледоступа обслуживать десятки тысяч пользователей, связанных с центром с помощью персональных компьютеров, рабочих станций и локальных линий связи.

Современные региональные вычислительные центры в США имеют общую производительность в десятки миллиардов операций в секунду и обслуживают тысячи пользователей.

### Литература

- 1. Johnson G.M. Exploiting Parallelizm in Computational Science. North-Holland, Future Generation Computer Systems, 1989, 5, pp 319-337.

- 2. Van der Steen Aad J. Overview of Recent Supercomputers. The Netherlands, Academic Computing Centre Utrecht, 1994, 47 p.

- 3. Бурцев В.С. Система массового параллелизма с автоматическим распределением аппаратных средств суперЭВМ в процессе решения задачи. Юбилейный сборник трудов институтов Отделения информатики, вычислительной техники и автоматизации РАН, Москва, 1993, том II, стр 5-27.

- 4. Бурцев В.С. Тенденции развития высокопроизводительных систем и многопроцессорные вычислительные комплексы. Москва, 1977, 28 стр. (Препринт ИТМ и ВТ АН СССР)

- 5. Бурцев В.С., Кривошеев Е.А., Асриэли В.Д., Борисов П.В., Трегубое К.Я. Векторный процессор МВК "Эльбрус-2". СуперЭВМ, 1989, сборник научных трудов ОВМ АН СССР.

- 6. Отчет по ОСВМ. ВЦКП РАН, 1992.

## Новые подходы к оценке качества вычислительных средств

### В.С.Бурцев

#### Аннотация

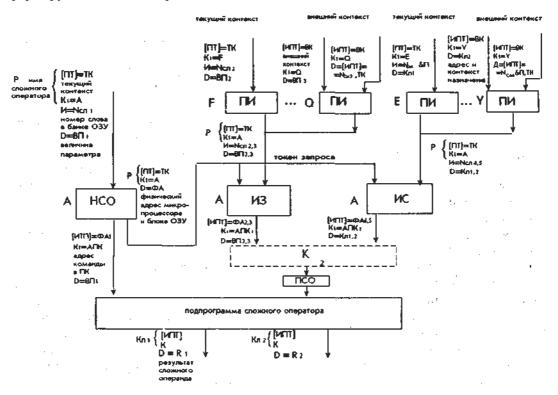

В статье даются новые методы оценки структурных и архитектурных решений вычислительных средств. Проводится анализ современных высокопроизводительных многопроцессорных систем и многомашинных вычислительных комплексов. Делается вывод о том, что развитие вычислительных средств в настоящее время переживает определенный кризис, связанный с использованием в высокопараллельных структурах традиционного фон-Неймановского принципа организации вычислительного процесса. Делается вывод о необходимости перехода к созданию новых архитектур на суперпроцессорах, работающих на новых принципах и обладающих производительностью  $10^{11}$ - $10^{12}$  on/с каждый.

Традиционно принято оценивать производительность вычислительных средств по скорости выполнения ими набора типовых тестовых задач. Это, безусловно, самый эффективный метод оценки производительности вычислительных комплексов, так как наряду с аппаратными средствами он в какой-то мере оценивает и эффективность системных программ. Однако, метод тестовых задач не учитывает времени затраченного программистом на подготовку этих задач. Нет так же ответа и на вопрос о возможности использования подобных вычислительных комплексов в открытых системах, так как этот метод не оценивает те сложности, которые возникнут в той или иной архитектуре при создании системного матобеспечения, работающего с открытыми системами. Метод не учитывает и квалификации программиста, реализующего адаптацию тестовой задачи к испытуемой аппаратуре. Поэтому результат тестирования зависит от многих факторов, вносящих в это процесс существенные искажения. Таким образом, этот метод не отвечает на целый ряд принципиальных вопросов, связанных с решением на современных комплексах сложных

проблемных задач, работающих над большим объемом взаимосвязанных данных. А именно ради решения таких задач создаются многомашинные и многопроцессорные средства.

Как известно [1], для решения целого ряда проблемных задач требуется производительность  $10^{11}$ - $10^{13}$  оп/с при работе с общей оперативной памятью объемом в  $10^9$ - $10^{10}$  слов. При современном состоянии развития вычислительной техники для решения этих задач потребуется сотни параллельно работающих процессоров.

Все это говорит о том, что должны быть созданы некоторые дополнительные оценки вычислительных средств, в какой-то мере отвечающие на эти вопросы. Нельзя сказать, что таких оценок по архитектуре и параметрам вычислительных средств не было вообще. Так пользователь и системный программист знали, что среди однопроцессорных машин лучшей является та, которая имеет большую производительность процессора, больший объем оперативной и внешней памяти, большую пропускную способность данных между оперативной и внешней памятью и т.д.

Однако, не существовало в какой-то мере систематизированной системы оценок даже для однопроцессорных систем, не говоря о многопроцессорных и многомашинных комплексах.

Попробуем на базе имеющихся в настоящее время общеизвестных суждений и эмпирических данных создать некую систему качественных сравнительных оценок вычислительных средств в интересах как системных программистов, так и программистов-пользователей. В настоящее время в промышленном выпуске существуют всего три архитектуры вычислительных средств: однопроцессорные машины, включая векторные конвейерные; многопроцессорные системы и многомашинные вычислительные комплексы [2]. В первую очередь дадим сравнительные оценки основных особенностей трех структур. Безусловно, с точки зрения простоты загрузки этих структур однопроцессорные машины имеют неоспоримое преимущество перед остальными. Действительно, и последовательные, и параллельные алгоритмы вычислительных процессов без особой изобретательности программиста достаточно эффективно выполняются на однопроцессорных машинах. Исключение составляют векторные конвейерные системы, для которых необходимо, чтобы количество параллельных вычислительных процессов выполняемой задачи, включая векторные, было больше коэффициента конвейеризации системы Ск, где Ск - глубина конвейеризации системы, измеряемая числом команд, одновременно находящихся в системе и выполняющихся на различных уровнях ее конвейера.

Для загрузки многопроцессорной системы к алгоритму необходимо предъявить определенные требования параллелизма вычислительного процесса, а именно: количество параллельно выполняемых процессов Р должно быть больше числа параллельно работающих процессоров системы на протяжении всего времени выполнения задачи. Необходимо отметить, что обмен данными между процессами в этих системах происходит посредством обычного обращения процессоров к общему ОЗУ, а общая синхронизация по данным реализуется на уровне специальных команд [3].

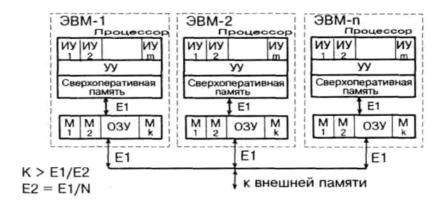

Многомашинные комплексы накладывают условия по параллелизму выполняемого алгоритма, аналогичные многопроцессорным, однако задачи межпроцессорного обмена (в данном случае межмашинные обмены) решаются гораздо сложнее - посредством взаимодействия операционных систем одной или нескольких машин. В то же время максимальное количество машин в таких комплексах может быть значительно большим, нежели количество процессоров в межпроцессорном комплексе. Последнее будет пояснено ниже.

Итак, из грубого анализа трех архитектур можно сделать следующий вывод. Если производительность однопроцессорного комплекса достаточна для решения задачи - необходимо использовать однопроцессорный. При одинаковом числе процессоров в многопроцессорной системе или машин в многомашинном комплексе, достаточном по производительности для выполнения задач, надо отдавать предпочтение многопроцессорной системе. И только в том случае, когда многопроцессорный комплекс при максимальном количестве процессоров не удовлетворяет по производительности, необходимо использовать многомашинный комплекс.

Это грубый анализ трех структур вычислительных средств. На самом деле на практике стоит вопрос не только определения глобальной архитектуры вычислительного комплекса, но и вопрос конкретного выбора вычислительных средств внутри одной и той же архитектуры. Несколько более глубокий сравнительный анализ отдельных машин, систем и комплексов должен идти по линии наиболее важных параметров каждого из них и их взаимной увязки.

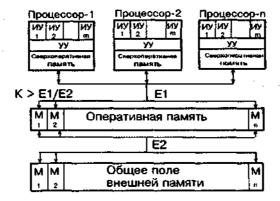

Так. однопроиессорных машин такими параметрами производительность процессора (Ппр), пропускная способность канала процессор-ОЗУ (Епр), объем ОЗУ (Q) и пропускная способность ОЗУ-внешняя память Е (последняя ограничивается в основном скоростью внешней памяти). Максимальная производительность однопроцессорной машины, как правило, ограничивается частотными характеристиками используемой элементной базы и соединений. Как правило, для всех систем выполняется следующее соотношение: Ппр=REпр, где R процент обращений процессора к ОЗУ из всех обращений его за данными. Подразумевается, что большая часть обращений за данными идет в сверхоперативную память процессора (быстрые регистры, КЭШ и т.д.). Учитывая, что среднее число обращений за данными на одну операцию равно 2, а процент обращений к ОЗУ колеблется от 0,8 до 0,98 в зависимости от структуры задачи, можно с достаточной для наших рассуждений точностью считать Ппр=Епр, где Ппр имеет размерность Mflops, а Епр - MB/s. Поэтому, если мы не располагаем значениями Епр, можно определять их через Ппр. Производительность векторных конвейерных процессоров в дополнение к этому зависит от глубины конвейеризации, реализованной в процессоре. Опыт конструирования этих процессоров и анализ реальных задач показывает, что увеличение производительности процессора за счет конвейеризации не выше одного порядка.

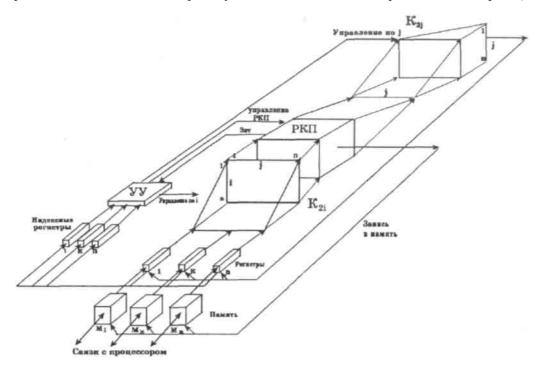

*Многопроцессорная система* имеет следующие основные параметры: число процессоров N, производительность процессора  $\Pi$ пр, пропускная способность коммутатора между процессорами и ОЗУ Eк, пропускная способность ОЗУ-внешняя память E. Во многих случаях Eк = NEnp =  $N\Pi$ np

Максимальная производительность многопроцессорной системы ограничивается двумя факторами: пропускной способностью коммутатора между процессорами - ОЗУ (Ек) и требованием корректной работы припроцессорной КЭШ памяти. И та, и другая причины не позволяют строить многопроцессорные комплексы с большим количеством процессоров N. Аппаратная сложность коммутатора пропорциональна N<sup>2</sup>. С увеличением сложности коммутатора растут временные задержки при обращении процессора к ОЗУ, что снижает скорость работы каждого процессора даже при наличии КЭШ при каждом процессоре. Практически увеличение числа процессоров выше 32 в одном коммутаторе вряд ли целесообразно. Исключение припроцессорной КЭШ памяти приведет к увеличению числа обращений процессоров к ОЗУ, что еще больше ограничит величину N. Обеспечение корректности работы КЭШ в многопроцессорной системе - сложная задача, и качество ее решения, в свою очередь влияет на производительность всей системы, особенно при больших N. Дело в том, что если два процессора поработали с общими данными, даже в том случае, когда синхронизация по данным для них была выполнена правильно, в КЭШ одного из процессоров могут сохраняться старые данные. При этом процессор, работая с обновленными другим процессором общими данными, может часть данных брать из ОЗУ (новые), а часть из КЭШ (старые). Корректность вычислительного процесса в этом случае будет нарушена. Простейшее решение проблемы корректности работы КЭШ в многопроцессорных системах состоит в том, что при каждой записи процессора в ОЗУ должно быть обеспечено стирание данных, записанных по этому адресу в КЭШ всех процессоров. Естественно, этот способ не позволяет увеличить число процессоров в многопроцессорных системах без значительного падения ее производительности. Наиболее эффективно эта задача была решена в МВК "Эльбрус", где число процессоров, одновременно работающих на общей памяти, было увеличено до 16 практически без потери производительности. Причем, способ обеспечения корректности КЭШ, реализованный в МВК "Эльбрус", практически инвариантен к числу процессоров системы - каждый процессор решает эту задачу самостоятельно без взаимодействия с соседними процессорами. Поэтому наиболее принципиальным препятствием в увеличении производительности многопроцессорных комплексов является коммутатор процессоры - ОЗУ.

Многомашинный комплекс должен решать достаточно сложную проблему обмена информацией между машинами, что осуществляется через взаимодействие операционных систем. Поэтому обмен информацией между машинами ведется, как правило, достаточно большими пакетами. Обмен малыми пакетами неэффективен из-за больших временных потерь, приведенных к одному слову. Может создаться впечатление, что проблема, подобная корректности КЭШ, в многомашинных комплексах отсутствует. На самом деле эта проблема при работе многих машин с общими данными переходит на уровень системных и пользовательских программ, что безусловно осложняет программирование задачи и увеличивает время ее выполнения. В то же время требования к временным параметрам системы коммутации машин становятся не такими жесткими, как в многопроцессорных комплексах, благодаря чему можно строить системы с большим числом машин N.

После такого общего анализа попробуем определить те параметры комплексов, которые накладывают определенные требования на системные программы и программы пользователей, имея в виду эффективное использование их аппаратных средств.

Начнем с однопроцессорной машины. Условием ее эффективного использования может служить критерий загрузки процессора. Для обеспечения загрузки однопроцессорной машины должно быть выполнено следующее неравенство на протяжении всего времени решения задачи:

$$Eпр/E$$

≤ Ко при объеме памяти ОЗУ Q, (1)

где Ko - средний процент переиспользования адресов ОЗУ на участке задачи объемом Q.

Действительно, если неравенство (1) не выполняется, то через определенное время производительность однопроцессорной машины будет определяться не величиной Епр, а Е, то есть пропускной способностью внешних устройств. Для того, чтобы этого не случилось, программист должен разбивать задачу на такие локальные части, для которых в объеме ОЗУ, равном Q, средний процент переиспользования адресов локальной части задачи, подкаченной в ОЗУ, превосходил величину Ко. Назовем величину Ко коэффициентом локализации. Естественно, чем больше объем памяти однопроцессорной машины Q, тем легче выполнить это требование. Поэтому условия выполнения неравенства (1) должны зависеть определенным образом от объема оперативной памяти. Примем некоторый объем ОЗУ Од, определенный практикой, за достаточный для локализации данных в ОЗУ. В этом случае для машин с памятью Q, меньшей Qд, усложняется проблема локализации данных, что может быть учтено соотношением (Qд/Q + 1), уточняющим неравенство (1):

$$\operatorname{Enp}\left(\operatorname{Qz}/\operatorname{Q}+1\right)/\operatorname{E} \leq \operatorname{K} o \tag{2}$$

B многопроцессорных системах условия обеспечения процессоров данными описывается подобным соотношением, в котором Епр заменяется величиной пропускной способности коммутатора процессоров - ОЗУ Ек (Ек = NEnp = NПпр). Предполагается, что все N процессоров имеют равную производительность Ппр и пропускную способность Епр. Тогда:

$$Kмп \ge E\kappa (Qд/Q + 1)/E$$

Здесь Q - объем ОЗУ всего многопроцессорного комплекса, а Qд сохраняет прежнюю величину, так как мы фактически как бы увеличили производительность процессора однопроцессорной машины в N раз.

Однако для многопроцессорных систем появляется еще одно необходимое условие их эффективного использования. На протяжении времени выполнения всей задачи должно соблюдаться следующее неравенство:

$$P>N$$

.

где Р - число параллельно выполняемых процессов.

Необходимо отметить, что для мультипрограммного режима работы многопроцессорной системы это неравенство при достаточном количестве задач

выполняется без особых усилий. В то же время при решении больших задач, у которых N велико, оно не всегда может быть реализовано, что приводит к неэффективной загрузке системы. Поэтому, чем больше число процессоров в многопроцессорной системе, тем более специализированной она является [2].

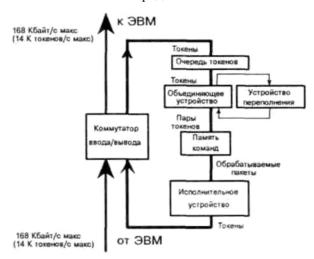

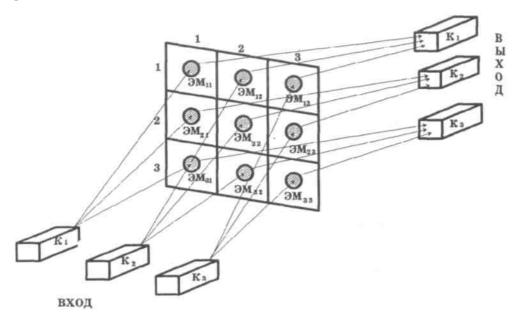

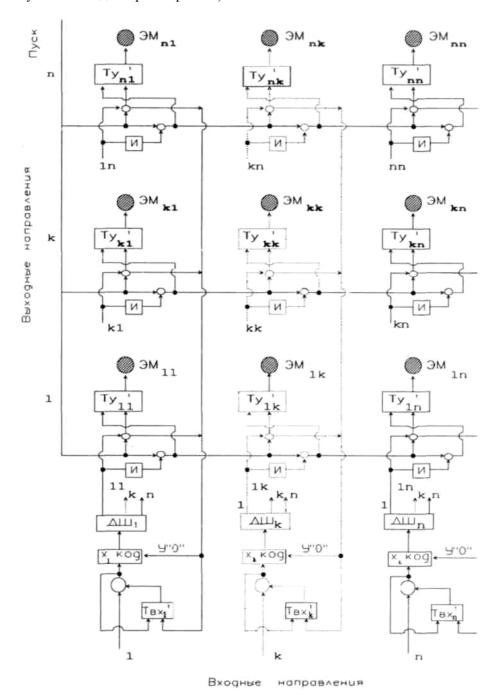

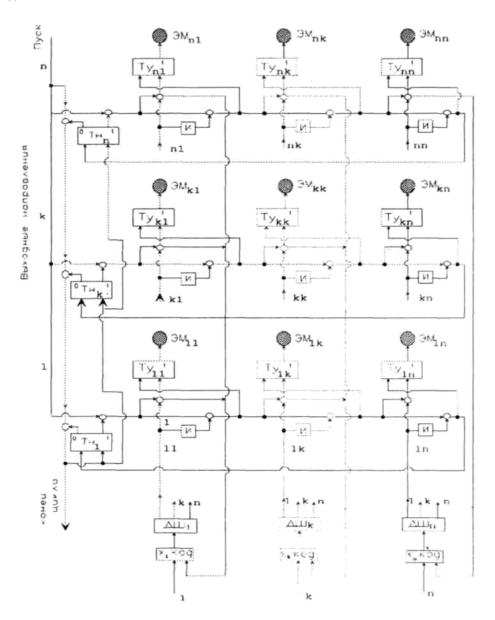

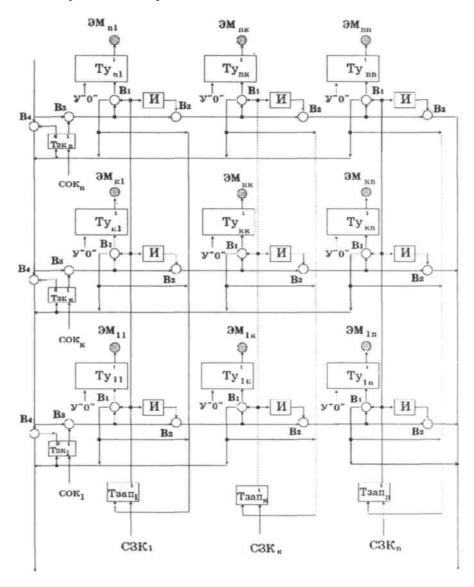

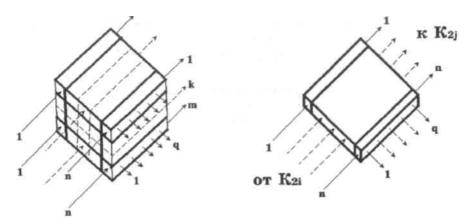

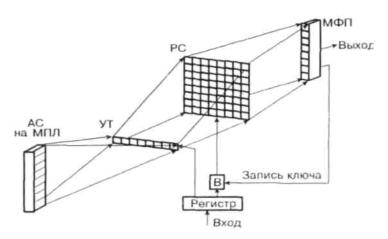

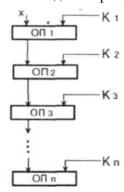

Для многомашинных комплексов требования полной загрузки системы описываются несколько сложнее. Прежде всего, необходимо рассмотреть возможности выполнения межмашинного обмена с точки зрения эффективной загрузки узла комплекса. Каждый узел многомашинного комплекса можно представить в виде одного или нескольких процессоров, ОЗУ и коммутатора, связывающего этот узел с другими узлами комплекса (Рис.1).

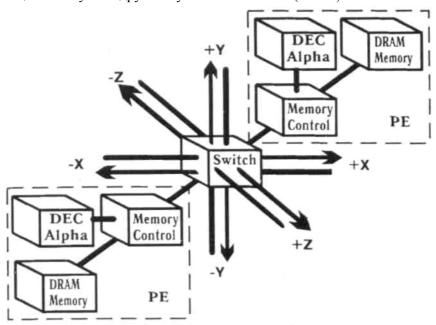

Рис.1. Схема узла Стау ТЗД.

PE - процессорный элемент, Memory Control - устройство управления памятью. DRAM Memory - оперативная память, Switch - коммутатор

В этом случае необходимое условие загрузки процессора или процессоров узла может быть описано неравенством:

$$Kмy \ge NyEпр (Qд/Qy + 1)/Ey$$

где Еку - пропускная способность коммутатора узла со стороны процессоров, обычно равная NyEnp,

Ny - количество процессоров в узле,

Еу - общая пропускная способность коммутатора (узла) со стороны связи этого узла с другими узлами комплекса.

Необходимо отметить, что Qд имеет ту же величину, что и в предыдущем неравенстве, а Qy - объем памяти узла. Это обстоятельство сильно усложняет задачу удовлетворения этого неравенства. В дополнение к этому для относительной

оценки межмашинного обмена той или иной системы необходимо ввести коэффициент, отражающий топологию связей многомашинных комплексов.

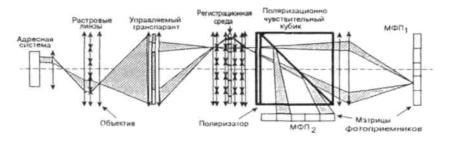

Рис.2. Схемы коммутации микропроцессоров в многомашинных комплексах.

В настоящее время реализованы следующие системы связей в многомашинных комплексах: "точка-точка", плоская матрица, трехмерная коммутация и система связей "гиперкуб" (Рис.2). Возможной характеристикой топологии связи может быть параметр, определяющий среднее число узлов передачи информации от узла к узлу. Так для системы "точка-точка" этот параметр b равен 1,

для транспьютерных связей  $b=1/2\sqrt{N}$  (рассматриваются транспьютерные

замкнутые системы), для трехмерной коммутации  $b = 3/4\sqrt[3]{N}$  (Cray T3D и T3E), для гиперкуба  $b = 1/2 \log_2 N$  (Ncube 2). Для конкретных систем эти формулы могут несколько корректироваться, однако порядок зависимости параметра b от N останется тем же, и при сравнении многомашинных комплексов он должен быть учтен b определении величины b в этом случае неравенство (2) уточниться следующим образом:

Условие загрузки многомашинного комплекса при взаимодействии с внешней памятью может быть описано следующим соотношением:

$$K_M \ge E_{MK} (Q_{\pi}/Q_M + 1)/E$$

,

P > N

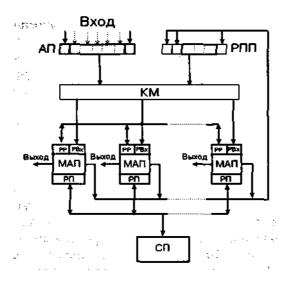

Таблица 1. Соотношения для дополнительной оценки комплексов

| Размер-<br>ность                  | E - MB/s                                                                                | 2<br>E - MB/s                                                          | 3<br>Π <sub>πp</sub> - MFls                          | $_{\rm H}$ $_{\rm H}$ $_{\rm H}$  | 5                                                                            |

|-----------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------|------------------------------------------------------|-----------------------------------|------------------------------------------------------------------------------|

| величин                           | Q - GB                                                                                  | Q - GB $\Pi_{\Pi P}$ - MFls                                            | Q - GB                                               | $\Pi_{\Pi P}$ -MFls               |                                                                              |

| Однопро-<br>цессорная<br>машина   | $K_0 \ge \frac{E_{np}}{E} \left( \frac{Q_A}{Q} + 1 \right)$                             |                                                                        | $K_{0\Pi} = \frac{\mathbf{Q}_{\Pi} \Pi_{np}}{Q} + 1$ | $Knp = \frac{\Pi_{9m}}{\Pi_{np}}$ | $K_{\text{OP E3}}=$ $=K_{\text{O}}K_{\text{OH}}K_{\text{HP}}$                |

| Многопро-<br>цессорная<br>система | $K_{MT} \ge \frac{NE_{np}}{E} \left( \frac{Q_A}{Q} + 1 \right)$                         |                                                                        | $K_{KIII} = \frac{Q_{II}^{NII}_{np}}{Q_{M}} + 1$     | $Knp = \frac{\Pi_{9m}}{\Pi_{np}}$ | $K_{\text{MII pe3}} =$ $= K_{\text{MII}} K_{\text{MTII}} K_{\text{np}}$      |

| Многома-<br>шинный<br>комплекс    | $ K_{MV}  \ge \frac{b^{N} {}_{y} E_{np}}{E_{y}} \left( \frac{Q_{x}}{Q_{y}} + 1 \right)$ | $K_{M} = \frac{NE_{np}}{E_{M}} \left( \frac{Q_{M}}{Q_{M}} + 1 \right)$ | $K_{MMI} = \frac{Q_{II} N\Pi_{np}}{Q_{M}} + 1$       | $Knp = \frac{\Pi_{9m}}{\Pi_{np}}$ | $K_{\text{M pes}}=$ $=K_{\text{My}}K_{\text{M}}K_{\text{M}\Pi}K_{\text{np}}$ |

Важное значение при сравнении вычислительных комплексов имеет такой элементарный параметр, как относительное быстродействие процессора или микропроцессора системы  $\text{Кпр} = \Pi \text{эт}/\Pi$ . Здесь  $\Pi \text{эт}$  - производительность микропроцессора, принятая за эталонную, которая выбирается как средняя

величина производительностей нескольких процессоров последнего выпуска Другим параметром является коэффициент достаточности памяти. Естественно, что чем меньше Кпр, тем ниже требования к распараллеливанию алгоритма для одной и той же задачи.

Практика использования вычислительных средств выявила следующую закономерность соотношения объема памяти и производительности системы  $Q_n$ , которая сохраняется на протяжении всего времени существования дискретных вычислительных средств - на каждый миллион операций в секунду приходится порядка 100 тысяч слов памяти ( $\approx 0.5$  MB). Естественно, чем больше память, тем удобнее программировать задачу и повышать загрузку процессоров. Поэтому можно ввести специальный коэффициент, учитывающий достаточность памяти: в однопроцессорной машине Kon = 0.5 Imp/Q + 1; в многопроцессорной системе  $Empirement{Kmn} = 0.5$  Imp/Q + 1; для многомашинного комплекса  $Empirement{Kmn} = 0.5$  Imp/Q + 1. В этих соотношениях Imp имеет размерность  $Empirement{Mflops}$ , а память  $Empirement{Q}$  Imp/Q + 1. В этих соотношениях Imp имеет размерность  $Empirement{Mflops}$ , а память  $Empirement{Q}$  Imp/Q + 1.

В Таблице 1 приведены все соотношения, по которым могут быть дополнительно оценены комплексы с точки зрения возможности их эффективного использования на разнообразных задачах пользователя. Другими словами, эти соотношения характеризуют сложность программирования на тех или иных системах, имея в виду, есть стремление достичь максимальной производительности вычислительных средств на решаемой задаче. Чем меньшие значения имеют правые части этих соотношений, тем легче выполнить условие полной загрузки системы. Произведение этих коэффициентов может дать качественную характеристику всего комплекса по эффективности его использования на различных классах задач. Для такой интегральной оценки необходимо правильно выбрать значения Qд и Пэт, так как они могут влиять на весовые характеристики этих коэффициентов. Анализ решения больших задач показывает, что для многих из них локализация данных во многих случаях может быть выполнена на объеме памяти Qд = 1 GB. Величина Пэт, как уже говорилось, может быть выбрана исходя из средней производительности процессора сегодняшнего дня lGFlops.

Приведенные оценки качества вычислительных комплексов указывают только возможные принципы нового подхода к анализу вычислительных средств при их выборе для использования в тех или иных сферах деятельности. Неполнота приведенных соотношений заключается прежде всего в том, что при определении пропускной способности канала процессор - ОЗУ не учитываются особенности построения сверхоперативной памяти (быстрые регистры, КЭШ, различные буферные устройства и т.д.). При определении пропускной способности между ОЗУ и внешней памятью не учитываются реальные возможности внешних устройств и телекоммуникационных систем, выходящих на вычислительные средства, и т.д. Однако, принципы развития и уточнения этих оценок достаточно ясны и могут быть без труда найдены для каждого конкретного случая.

Привлекательность приведенных оценок состоит в том, что все эти коэффициенты могут быть легко рассчитаны на основании рекламных данных, выдаваемых

фирмами. В качестве примера приведем анализ некоторых современных многопроцессорных систем и многомашинных комплексов.

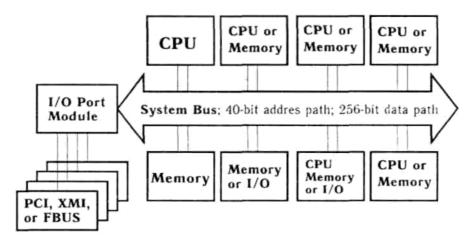

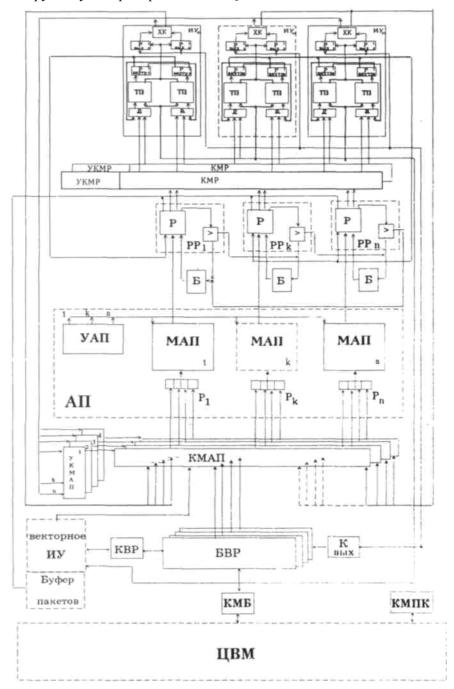

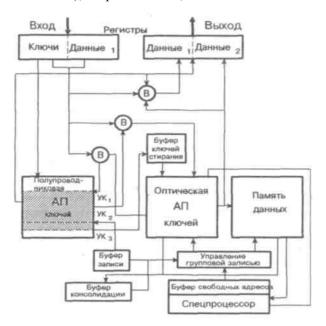

Многопроцессорные системы имеют две различные структуры в зависимости от схемы построения коммутатора. Одна из них использует для коммутации данных общую шину, как, например, сервер фирмы DEC (Рис.3), другая -бесконфликтный коммутатор типа "каждый с каждым".

Рис.3. Структурная схема сервера AlphaServer 8400.

CPU - Процессор; Memory - Память; I/O Port Module - Модуль связи с устройствами ввода/вывода: System Bus - Общая системная шина; I/O - Ввод/вывод; PCI, XMI, FBUS - Интерфейсы ввода/ вывода.

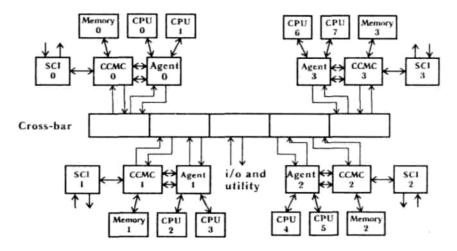

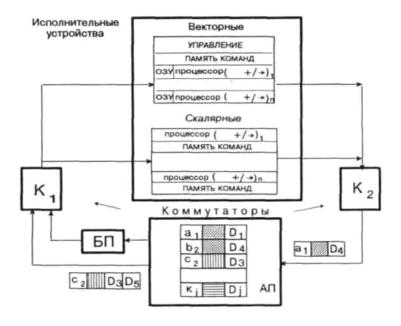

Примером последней структуры может служить многопроцессорный комплекс SPP-1200 фирмы Convex при коммутации микропроцессоров внутри кластеров (Hypernode) (Puc.4).

Рис.4. Структурная схема узла SPP 1200 фирмы Convex.

Cross-bar - коммутатор каждый с каждым (5x5); CPU - процессор; Memory - память; CCMC - локальный коммутатор процессор-память; SCL - локальный адаптер межузловой сети; Agent - адаптер; i/o and utility - ввод/вывод.

Многомашинные комплексы также отличаются структурой коммутатора: комплекс SP-2 имеет структуру коммутатора типа "точка-точка"; транспьютерные системы, выпускаемые НПО "Квант" (Россия) - структуру типа матрицы; в Cray T3D и T3E коммутатор организован по принципу трехмерного торроидального куба; а NCube 2 - по структуре гиперкуба. Особенности коммутации этих многомашинных комплексов в наших соотношениях учитываются коэффициентом b (Рис.2).

Результаты анализа многопроцессорных систем фирмы Convex (SPP-1200, SPP-2000), фирмы DEC (Server8400) и фирмы Cray (j916, C-90 и T-90) приведены в Таблице 2.

Таблица 2. Многопроцессорные системы (распределяемая память)

| Фир-<br>ма | 7.00           | Базов<br>проце        |          |                         |    | раме<br>стер   |              |           |         | загру | Коэффициент<br>эффективности<br>загрузки |     | R=               | Примечания            |                                                                    |

|------------|----------------|-----------------------|----------|-------------------------|----|----------------|--------------|-----------|---------|-------|------------------------------------------|-----|------------------|-----------------------|--------------------------------------------------------------------|

|            |                | Наны<br>ено-<br>ванне | Г<br>МГц | Π <sub>αρ</sub><br>GFIs | N  | Emp<br>GB<br>s | E<br>GB<br>s | P<br>CiPs | Q<br>GB | Кмп   | KMIII                                    | Кпр | K <sub>pen</sub> | K <sub>pes</sub><br>P |                                                                    |

| CONVEX     | SPP.<br>1200   | PA-<br>7200           | 120      | 0.24                    | 8  | I              | 0.27         | 1.9       | 2       | 5.5   | 1.5                                      | 4   | 33               | 4                     | На аппаратно - программном<br>уровне поддерживается<br>объединение |

| CONVEX     |                | PA-<br>8000           | 180      | 0.7                     | 16 | 7.6            | 1.72         | 112       | 4       | 4     | 2                                        | 1   | 8                | 0.7                   | до 32 кластеров<br>с коррекцией КЭШ                                |

| DEC        | Server<br>8400 | Alpha<br>21164        | 300      | 0.5                     | 12 | 2.4            | 12           | 6.0       | 3       | 2     | 2                                        | 2   | 8                | 1.3                   |                                                                    |

| Cray       | Cray<br>3916   | Набор                 | 100      | 0.2                     | 16 | 26             | 1.6          | 3.2       | 4       | 16    | 1                                        | 5   | 80               | 26                    |                                                                    |

| Cray       | Cray<br>C 90   | Набор                 | 240      | 1                       | 16 | 245            | 13.6         | 16        | 8       | 18    | 1                                        | 1   | 18               | 1.1                   |                                                                    |