Информационно-вычислительная система

Описание изобретения к авторскому свидетельству

Авторы изобретения: В.А. Мельников, А.А. Соколов, В.И. Смирнов, М.В. Тяпкин, Л.А. Зак, Ю.И. Митропольский, Ю. Н. Знаменский, В. А. Жуковский, В.Ф. Жиров, В.Л. Ли, Л.Н. Королев, В.П. Иванников, А.Н. Томилин, Г.В. Степанов, А.И. Журавлев, А.В. Аваев и В.С. Новизенцев

Изобретение относится к области вычислительной техники.

Известны информационно-вычислительные системы, объединяющиеся на основе общей памяти, имеющей несколько параллельных выходов, к которым присоединяются центральные и периферийные процессоры и блоки памяти.

Устройства сопряжения, которыми оборудованы устройства, входящие в систему, ограничивают минимальный размер системы. Если набор устройств составляет не максимальный вариант системы, часть дополнительной аппаратуры не используется.

В известных системах устройства сопряжения высокопроизводительных устройств не унифицированы. В каждом случае решается вопрос о подключении одного или группы определенных устройств к конкретной схеме. Это требует дополнительного оборудования и уменьшает возможность изменения структуры системы. Обмену данными через устройство сопряжения предшествует обмен служебной информацией, которая устанавливает связь. Это снижает скорость работы системы.

Устройства сопряжения внешних устройств являются унифицированными для одной или даже группы систем, в известных системах они обладают рядом недостатков.

Во-первых, информация передается только в стартстопном режиме, что существенно ограничивает пропускную способность устройства сопряжения, особенно при значительном удалении устройств друг от друга.

Во-вторых, для учета влияния передаваемых данных на выполнение алгоритма обмена, которое должно быть учтено в истинном масштабе времени, необходимо участие центрального процессора. Это приводит к потере его производительности или производительности всей системы.

В-третьих, в каждый момент времени возможен обмен информацией только двух абонентов, что снижает производительность системы.

В-четвертых, устройства сопряжения не симметричны, т. е. набор шин и алгоритм работы зависят от места включения устройства, управляющего обменом. Это снижает гибкость структуры системы и ее надежность.

Целью изобретения является повышение производительности и надежности системы и экономия оборудования. Указанная цель достигается за счет того, что информационно-вычислительная система содержит устройство унифицированного сопряжения, объединяющее высокопроизводительные устройства и устройство унифицированного сопряжения, объединяющее внешние устройства.

Кроме того, устройство сопряжения высокопроизводительных устройств содержит шины данных, шины адресов отправителя и адресата, шины синхронизации и сеть коммутации на 2m направлений (m — количество разрядов адреса устройства, участвующего в обмене), состоящую из коммутаторов, имеющих l =3/2m направлений, при этом каждый коммутатор имеет для каждого направления блоки приема сообщений, входы которых соединены с шинами обмена, блоки синхронизации, блоки контроля по четности, блоки защиты, блоки преобразования адреса, блоки дешифрации, блоки очередности коммутации, регистры, блоки выдачи сообщений, выходы которых соединены с шинами обмена, блок работы с диспетчером, блок управления коммутацией, причем первые выходы блоков приема сообщений соединены с первыми входами каждого регистра; вторые выходы блоков приема сообщений соединены со входами соответствующих блоков синхронизации и блоков преобразования адреса, со входами блока работы с диспетчером и со входами соответствующих блоков защиты и блоков контроля по четности, выходы которых соединены с соответствующими входами блока работы с диспетчером; первый выход блока работы с диспетчером соединен с первыми входами блоков выдачи сообщений, вторые входы которых подключены к выходам соответствующих регистров; второй выход блока работы с диспетчером соединен с первыми входами блоков дешифрации, вторые и третьи входы которых соединены соответственно с выходами блоков преобразования адреса и блоков синхронизации; выходы каждого блока дешифрации соединены со входами каждого блока очередности коммутации, выходы которых соединены со входами блока управления коммутацией, выход блока управления коммутацией соединен со вторыми входами регистров.

Устройство унифицированного сопряжения внешних устройств содержит шины данных, шины идентификатора, шины контроля, шины синхронизации и сеть коммутаций на 2n+1 направлений (n —количество разрядов адреса внешнего устройства), состоящую из коммутаторов, имеющих p=3/(2n +1) направлений, каждый коммутатор имеет для каждого направления блоки приема посылок, входы которых соединены с шинами обмена, блоки контроля идентификатора, блоки контроля по четности, блоки формирования запросов, блоки выдачи посылок, выходы которых подключены к шинам обмена, схемы готовности, блок определения очередности, блок формирования коммутирующего байта, блок управления коммутацией; причем первые выходы каждого блока приема посылок соединены с первыми входами каждого блока выдачи посылок за исключением блоков одного направления, со входами соответствующих блоков контроля по четности и блоков контроля идентификаторов, с первой группой входов блока определения очередности; вторые выходы блоков прием посылок соединены с первыми входами соответствующих блоков формирования запросов, вторые входы которых соединены с выходами соответствующих блоков контроля по четности, третьи блоков контроля идентификаторов, четвертые входы блоков приема посылок соединены с выходами соответствующих схем готовности; выходы блоков приема посылок соединены со второй группой входов блока определения очередности, выход которого соединен со входом блока формирования коммутирующего байта, первый выход которого соединен со вторыми входами блоков выдачи посылок, а второй выход — со входом блока управления коммутацией, причем первый его выход подключен к схемам готовности, а второй — к третьим входам блоков выдачи посылок,

Структура системы может быть, мультипроцессорной, т. е. такой, когда центральные и периферийные процессоры объединяются на основе общей памяти, агрегатной, т. е. такой, когда каждый процессор имеет собственную память и внешние устройства; также структура системы может быть смешанного типа. Каждому пользователю предоставляется система максимальной виртуальной конфигурации, а распределение действительных ресурсов между пользователями и учет действительной конфигурации информационно-вычислительной системы производится автоматически операционной системой, причем этот процесс упрощается и облегчается с помощью аппаратурных средств. Повышение надежности достигается путем резервирования устройств, а также организации многодоступности внешних устройств системы.

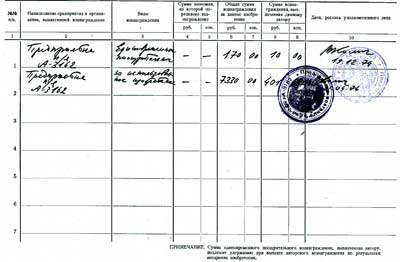

На фиг. 1 представлена структурная схема информационно-вычислительной системы, содержащая центральные процессоры 1—4, блоки памяти 5, 6 коммутаторы 7—11 устройства унифицированного сопряжения высокопроизводительных устройств, периферийные процессоры 12—15, коммутаторы 16—22 устройства унифицированного сопряжения внешних устройств, телеграфные мультиплексоры 23, 24, телефонные мультиплексоры 25, 26, вычислительную машину М-220 27, вычислительную машину БЭСМ-4 28, вынесенный пульт 29, устройство 30 ввода-вывода на перфокартах.

На фиг. 2 приведена функциональная схема коммутатора устройства унифицированного сопряжения высокопроизводительных устройств на четыре направления, содержащая блоки 31—34 выдачи сообщений, блок 35 управления коммутацией, блок 36 коммутации сообщений с регистрами 37—40, блоки 41—44 очередности- коммутации, блоки дешифрации 45—48, блоки 49—52 преобразования адреса, блоки 53 работы с диспетчером, блоки защиты 54—57, блоки контроля 58—61, блоки синхронизации 62—65, блоки 66—69 приема сообщений.

На фиг. 3 показана функциональная схема устройства унифицированного сопряжения внешних устройств на пять направлений, содержащая блоки 70—74 выдачи посылок, блок 5 формирования коммутирующего байта, блок 76 управлении коммутацией, блок 77 коммутации сообщений, схемы готовности 78— 82, блок 83 определения очередности, блоки 84—88 формирования запросов, блоки 89— 93 контроля идентификаторов, блоки 94—98 контроля по четности, блоки 99—103 приема посылок.

Высокопроизводительные устройства которыми являются центральные процессоры 1—4, блоки памяти 5, 6 и периферийные процессоры 12—15, обмениваются информацией через устройство унифицированного сопряжения высокопроизводительных устройств, состоящее из шин сопряжения и сети коммутация. двойной комплект шин обмена обеспечивает дуплексную работу устройств, а сеть коммутации — гибкое и экономное изменение конфигурации системы и соединение любых пар устройств.

Устройство унифицированного сопряжения высокопроизводительных устройств имеет следующие особенности.

1. Для экономии аппаратуры сеть коммутации состоит из отдельных коммутаторов, каждый из которых имеет меньше Направлений, чем вся сеть. Если сеть коммутаций имеет 2m направлений (m — количество разрядов адреса устройства, участвующего в обмене), то отдельный коммутатор может иметь от трех до 2m направлений, связанных по принципу «каждое с каждым». На фиг. 1 показана сеть коммутации, образованная коммутаторами (7, 8, 9, 10, 11), имеющими по четыре направления, объединяющая 10 устройств.

2. Для увеличения производительности системы при экономном расходовании оборудования:

а) обмен ведется однопосылочными сообщениями, содержащими как данные, так и адреса двух обменивающихся устройств, в стартстопном режиме с темпом до 2*106 слов в секунду; этим сокращается время ожидания коротких массивов сообщений необходимость передачи которых возникает «на фоне» длинных массивов;

б) путь обмена для каждого сообщения состоит из отдельных участков; участок характеризуется тем, что он начинается и оканчивается хранящим регистром: сигнал со входного регистра поступает до тех пор, пока он не будет принят на выходной регистр; в то время, как одним сообщением занят некоторый участок пути, остальные участки пути этого сообщения могут быть использованы другими сообщениями, передаваемыми по другим путям;

в) шины обмена и коммутаторы обеспечивают две одновременные симплексные связи для каждого устройства; возможна дуплексная связь пары устройств;

г) каждый коммутатор имеет 2m блоков преобразования адреса, разрядность которых определяется количеством направлений коммутатора. Содержимое блоков устанавливается с пульта управления или программой-диспетчером. Таким образом, в сообщении указывается не сумма участков, составляющих путь следования, а номер, закрепленный за устройством, в которое должно попасть сообщение. Блоки преобразования адреса направляют сообщение по нужному пути не только тогда, когда весь путь свободен, но и тогда, когда свободен хотя бы ближайший участок пути. Например, указанное в сообщении, исходящем из центрального процессора 1, адресата номер 4 означает, что блоки преобразования адреса обеспечат продвижение сообщения из коммутатора 9 в коммутатор 10, из него — в коммутатор 11, из него — в центральный процессор 4. Причем продвижение начнется, как только освободится участок: центральный процессор 1, коммутатор 9. Центральный процессор 4 может быть подключен к любому направлению сети коммутации. Соответствующим образом измененное содержимое блоков, преобразования адреса обеспечит продвижение сообщения от центрального процессора 1 к центральному процессору 4.

3. Для увеличения надежности системы при экономном расходовании оборудования:

а) каждый коммутатор осуществляет контроль сообщения по четности, а также проверяет, не адресовано ли сообщение к адресату, обращение к которому запрещено. Для блокировки устройств имеется 2m одноразрядных блоков защиты, управляемых программой-диспетчером. Сообщение проходит на выход коммутатора только в случае, если контроль по четности и проверка защиты не обнаружили ошибки;

б) устройство унифицированного сопряжения обеспечивает дуплексную связь любой пары устройств так, что все устройства являются полноправными и каждое устройство может с одинаковым успехом выполнять роль управляющего или управляемого устройства. С этой точки зрения безразлично, например, какому из центральных процессоров 1, 2, 3, 4 программно поручены функции диспетчера системы, ибо каждый центральный процессор может быть связан с любым устройством, например с периферийным процессором 12 может быть связан центральный процессор 1 через коммутаторы 9, 8, центральный процессор 2 — через коммутаторы 7, 8, центральные процессоры 3 и 4 — через коммутаторы 11, 10, 9, 8;

в) между устройствами существует больше одного пути обмена, например центральный процессор 1 связан с центральным процессором 2 не только через коммутаторы 9, 8 7, но и через коммутаторы 9, 10, 7.

Перечисленные особенности устройства унифицированного сопряжения высокопроизводительных устройств обеспечиваются тем, что коммутаторы объединяются в сеть коммутации, а она, в свою очередь, соединяется со всеми устройствами шинами обмена, содержащими шины данных, шины адресов отправителя и адресата, шины синхронизации, и соответствующим построением коммутаторов.

Рассмотрим подробнее схему коммутатора устройства унифицированного сопряжения высокопроизводительных устройств (фиг. 2).

Входные шины направлений соединены с блоками 66—69 приема сообщений, а выходные шины — с блоками 31—34 выдачи сообщений, каждый из которых связан со своим регистром 37—40 блока 36 коммутации сообщений и с блоком 53 работы с диспетчером. Блоки 66—69 приема сообщений подключены к регистрам 37—40 по принципу «каждый к каждому». Кроме того, к регистрам 37—40 подключен блок 35 управления коммутацией. Второй выход каждого блока 66—69 присоединен к блокам контроля 58—61, к блокам защиты 54—57, к блокам 49—52 преобразования адреса, к блокам синхронизации 62—65, к блоку работы с диспетчером. Все блоки защиты 54— 57 и блоки контроля 58—6 1 соединены со входами блока 53 работы с диспетчером, который связан с блоками дешифрации 45—48. Входы каждого блока дешифрации связаны с соответствующими блоками 49—52 преобразования адреса и блоками 62—65 синхронизации. Выходы блоков дешифрации 45—48 соединены со входами блоков 41—44 очередности коммутации по принципу «каждый с каждым», а выходы блоков очередности коммутации — ко входу блока 35 управления коммутацией.

Таким образом, сообщение, поступившее на любой вход коммутатора, синхронизируется с тактирующей частотой коммутатора. Каждый блок защиты 54—57 проверяет, не указан ли в сообщении адресат, обращение к которому запрещено, а каждый блок контроля 58—61 осуществляет проверку каждого сообщения по модулю два. Кроме того, адрес абонента-адресата поступает в блоки 49—52 преобразования адреса.

Если не обнаружено обращения к запрещенному адресату и ошибки при контроле по четности, блок 53 работы с диспетчером разрешает прием в блоки дешифрации 45—48 из блоков 49—52 преобразования адреса и синхронизацию номера направления коммутатор а, соответствующего номеру адресата, указанному в сообщении. дешифрированный номер направления поступает в блок 35 управления коммутацией, который подключает соответствующий блок 66—69 приема сообщений к одному из регистров 37—40, соответствующему нужному направлению, если он занят предыдущим обращением. Одновременно соответствующий блок синхронизации 62—65 выдает ответный импульсный сигнал, разрешающий смену кода во входных шинах. Если регистр 37—40, соответствующий нужному выходу, занят, то сообщение выставляет запрос на обращение к этому регистру в его блок 41—44 очередности коммутации.

С регистра 37—40 сообщение через соответствующий блок 31—34 выдачи сообщений поступает на выходные шины. Вместе с сообщением выдается синхроимпульс, сигнализирующий о наличии нового сообщения.

Если в сообщении обнаружена ошибка почетности или запрещенное сообщение, блок 53 работы с диспетчером запрещает коммутацию такого состояния и передает диспетчеру адрес места обнаружения ошибки и сведения о ее характере.

Внешние устройства (фиг. 1) — вынесенный пульт 29, устройство 30 ввода-вывода на перфокартах, машина М-220 27, машина БЭСМ-4 28, телефонные и телеграфные аппараты (на чертеже не показаны), присоединяемые через линии связи группами с помощью телефонных 25, 26 и телеграфных 23, 24 мультиплексоров, и т. д., обмениваются данными с блоками памяти 5, 6, а некоторой управляющей информацией — с центральными процессорами 1—4 через устройство унифицированного сопряжения внешних устройств, которое допускает более экономное по аппаратуре объединение в систему значительно большего числа устройств и машин, расположенных на существенно большем расстоянии, чем это позволяет устройство унифицированного сопряжения высокопроизводительных устройств. Однако при этом обмен возможен с более низкой скоростью, чем через устройство унифицированного сопряжения высокопроизводительных устройств.

Устройство унифицированного сопряжения внешних устройств связывает периферийный процессор с внешними устройствами. К нему относятся шины обмена и сеть коммутации. Двойной комплект шин обмена обеспечивает дуплексную работу, сеть коммутации — гибкое изменение конфигурации системы и соединение любых пар устройств.

Основным форматом информации, передаваемой через устройство унифицированного сопряжения внешних устройств, является восьмиразрядный байт, который используется для передачи адресов, команд, данных, признаков состояния. Для указания рода информации служат шины идентификации.

Обмен информацией между двумя устройствами производится сообщениями. Сообщение содержит последовательно выдаваемые посылки, состоящие из байтов с их идентификаторами. Первая посылка в сообщении используется для указания пути обмена и называется коммутирующей. С ее помощью устанавливается связь. Последняя посылка содержит признак окончания сообщения и приводит к разрыву связи. Поскольку время коммутации зависит от состояния коммутаторов и устройств, коммутирующая посылка всегда передается в стартстопном режиме, т. е. выдача посылки, следующей за коммутирующей, производится только после получения синхроимпульса «Ответ».

Устройство унифицированного сопряжения внешних устройств имеет следующие особенности:

1. Для экономии аппаратуры сеть коммутации состоит из отдельных коммутаторов, каждый из которых имеет меньше направлений, чем вся сеть. Максимальное количество направлений сети коммутации определяется производительностью используемых внешних устройств и необходимым объемом оперативной памяти системы. Сеть коммутации имеет 2n+1 направление (n - количество разрядов адреса внешнего устройства), а отдельный коммутатор может иметь от трех до 2n+1 направление, связанных по принципу «каждое с каждым». Если считать единицей информации в устройстве унифицированного сопряжения восьмиразрядный байт (n=8) и требовать установления соединения одной посылкой, то каждый периферийный процессор 12, 13, 14, 15, может обслужить до 256 внешних устройств. Они могут подсоединяться к периферийному процессору через любое число коммутаторов в любой комбинации по числу направлений коммутаторов. При этом число направлений сети коммутаций не должно превышать 257, что соответствует (28+1). На фиг. 1 коммутаторы 16, 17, 18, 19, 20 имеют по девять направлений, а коммутаторы 21, 22 — по пять направлений. Одиночные внешние устройства 27, 28, 29, 30 подключены к периферийным процессорам 12—15 через цепочки из трех коммутаторов. Каждое из восьми направлений коммутаторов 16, 17, 18 обслуживает 32 внешних устройства, коммутаторов 19, 20— четыре устройства, каждое из четырех направлений коммутаторов 21, 22 — одно устройство. Телефонные и телеграфные линии связи объединены в группы по 32 соответствующими мультиплексорами. Каждая группа присоединена к периферийному процессору через один коммутатор.

2. Для увеличения производительности системы при экономном расходовании оборудования:

а) коммутирующая посылка задает путь только от обратившегося устройства к принимающему устройству, используя принцип относительной адресации входов и выходов. Входом является направление коммутатора, к которому присоединено обратившееся устройство, а выходом — направление, связанное с принимающим устройством. Принцип относительной адресации предполагает упорядоченное и фиксированное расположение всех входов и выходов один относительно другого. для определения адреса выхода относительно входа необходимо в принятом направлении (например, по часовой стрелке на фиг. 1) отсчитать его номер, начиная с соседнего с входом выхода коммутатора, причем этому выходу присвоить нулевой номер. Путь задается посредством указания тех выводов коммутаторов в том порядке, в котором сообщение должно пройти через коммутаторы. Например, на фиг. 1 путь от периферийного процессора 12 до вынесенного пульта 29 будет задан так: 4 3 1 или в двоичном виде 100 011 01.

Число разрядов коммутирующего байта, используемое в одном коммутаторе, зависит от числа направлений p коммутатора. Например, при p=9 это число равно трем при p=5 - двум. Группа разрядов, управляющая работой одного коммутатора, называется коммутирующей группой. Так как коммутирующий байт может содержать несколько таких групп, коммутирующей группой, используемой в данном коммутаторе, принято считать группу старших разрядов байта. После использования она преобразуется и переставляется из старших разрядов байта в младшие со сдвигом всех промежуточных разрядов. Это позволяет последовательно соединять коммутаторы с произвольным числом направлений.

Коммутирующая посылка обратного пути также использует принцип относительной адресации и формируется коммутаторами и принимающими устройствами в процессе прохождения прямой посылки. Обратный адрес через коммутатор равен дополнению кода прямого адреса до числа, равного p — 2. В коммутаторе 16 трехразрядная коммутирующая группа прямого адреса превращается в группу обратного адреса

Такой способ обеспечивает формирование обратного адреса для цепочки коммутаторов с произвольным числом направлений.

Передача в коммутирующей посылке только адреса принимающего устройства, который, дойдя до этого устройства, превращается в адрес обратившегося устройства, разделяет двухсторонний обмен между двумя устройствами на два односторонних обмена. Коммутация для каждого из них устанавливается только при готовности обоих устройств (если свободен путь). Это сокращает среднее время ожидания для других сообщений, имеющих общие участки пути с рассматриваемым. Кроме того, время ожидания (при занятом пути) сокращается блоком 83 определения очередности обслуживания внешних устройств. Например, в структуре, приведенной на фиг. 1, может одновременно возникнуть необходимость обслуживания периферийным процессором 12 машины М-220 (27) и периферийным процессором 13 - вынесенного пульта 29. Блок 83 определения очередности разрешит установку соединения по тому пути, который дольше не обслуживался (по входу, который дольше не обслуживался). Интервал времени связи начинается с момента разрешения установления связи для данного входа и кончается по сигналу «отбой» от устройства приемника;

б) обмен через устройство унифицированного сопряжения внешних устройств производится в стартстопном режиме по сообщениям, а внутри сообщения (по посылкам) в стартстопном режиме или после установки соединения в непрерывном режиме с темпом до 2*106 байтов в секунду. Непрерывный режим обмена возможен, если скорости устройств согласованы между собой или скорость работы принимающего устройства заведомо выше скорости работы обратившегося (выдающего) устройства. В этом случае синхроимпульс ((ответ» либо не формируется, либо формируется, но выдающее устройство на него не реагирует;

в) обмен данными между периферийными процессорами (12—15) и внешними устройствами может быть изменен или прекращен на основе предварительного анализа передаваемых данных в периферийном процессоре. При этом анализ осуществляется без прерывания работы обслуживаемого устройства;

т) шины обмена и коммутатора обеспечивают две одновременные симплексные связи для каждого устройства. Возможна дуплексная связь между двумя устройствами. Между разными парами устройств в каждом коммутаторе может одновременно существовать до (p-1)/2 связей.

3. Для увеличения надежности системы при экономном расходовании оборудования:

а) каждый коммутатор осуществляет контроль посылки по четности, а также проверяет правильность последовательности посылок в сообщении. С этой целью просматриваются идентификаторы всех посылок, Сообщение должно состоять из коммутирующей посылки, посылок данных и последней посылки данных. Признак запрещенного кода идентификатора или неправильной последовательности идентификаторов запоминается. Результат контроля по четности и контроля идентификаторов может быть выдан коммутатором по запросу диспетчера обменов через устройство унифицированного сопряжения внешних устройств или обслуживающего устройства;

б) при распределении средств системы адрес диспетчера обменов через устройство унифицированного сопряжения внешних устройств фиксируется в тех коммутаторах, которые управляются данным диспетчером. Адрес обслуживающего устройства фиксируется в каждом из обслуживаемых им устройств. Таким образом, осуществляется защита устройств от неправильных обращений. Кроме того, диспетчер может направлять свои сообщения любому устройству в любой момент, независимо от занятости устройства. С другой стороны, любое устройство, независимо от. его места в системе, может выдать специальное сообщение, которое коммутатором направляется диспетчеру; в) устройство унифицированного сопряжения обеспечивает дуплексную связь каждой пары устройств так, что к любому направлению может быть подключено обслуживающее устройство, в том числе и выполняющее функции диспетчера через устройство унифицированного сопряжения внешних обменов устройств и обслуживаемое устройство. Это дает возможность сменить диспетчера после обнаружения его неисправности или в результате вмешательства оператора. В первую очередь смена диспетчера связана с изменением в коммутаторах адреса диспетчера. Например, в качестве диспетчера могут использоваться периферийные процессоры 12, 13, 14, 15;

г) дуплексные устройства унифицированного сопряжения и наличие более одного пути обмена между устройствами обеспечивают многодоступность внешних устройств.

Указанные особенности устройства унифицированного сопряжения внешних устройств обеспечиваются тем, что коммутаторы объединяются в сеть коммутации, которая связывает внешние устройства с периферийными процессорами 12—15, шинами обмена, содержащими шины данных, шины идентификатора, шины контроля и шины синхронизации, а также со ответствующим построением коммутаторов.

Функциональная схема устройства унифицированного сопряжения внешних устройств на пять направлений представлена на фиг. 3.

Входные шины направлений соединены с блоками 99—103 приема посылок, а выходные шины — с блоками 70—74 выдачи посылок, каждый из которых связан с блоком 77 коммутации сообщений и с блоком 75 формирования коммутирующего байта. Блоки приема посылок целиком подключены через блок коммутации сообщений к блокам выдачи посылок по принципу «каждый к каждому». Отсутствует лишь связь внутри одного и того же направления. Кроме того, к блоку 77 подключен блок 76 управления коммутацией. Каждый блок 99—103 приема посылок присоединен к блоку 94—98 контроля по четности и к блоку 89—93 контроля идентификаторов. Блоки контроля по четности, блоки контроля идентификаторов, а также синхронизирующая часть и часть, содержащая коммутирующий байт, каждого блока 99—103 приема посылок соединены с соответствующим блоком 84— 88 формирования запросов. Кроме того, с ним связана соответствующая схема готовности 78—82. Все блоки формирования запросов присоединены к блоку 83 определения очередности, который связан с блоком 75 формирования коммутирующего байта и ко всем блокам приема посылок.

Кроме того, блок формирования коммутирующего байта подключен к блокам 70—74 выдачи посылок и к блоку 76 управления коммутацией, соединенному с блоком 71 коммутации сообщений и со всеми схемами готовности 78—82.

Работа коммутатора по какому-либо входу начинается с приема коммутирующей посылки. Коммутирующая группа принятого байта, длина которой определяется числом направлений коммутатора, и импульс синхронизации поступают в блок формирования запросов.

Если не обнаружено неправильного идентификатора и ошибки при контроле по четности, если запрашиваемый выход свободен, выдается запрос. Из всех запросов выбирается старший в данный момент, для него переформированный коммутирующий байт выдается в нужный блок 70—74 выдачи посылок, устанавливается связь его с блоком приема посылки и гасится сигнал готовности выбранного направления. После установления связи по всему пути по синхроимпульсу «ответ» выдающее устройство начинает передавать дальнейшую часть сообщения без изменения коммутации. При этом коммутатор является для коммутированного пути простым ретранслятором сообщения. Передача части сообщения, содержащей данные, может вестись в стартстопном или непрерывном режиме. Установленная связь разрывается по сигналу «отбой», приходящему из принимающего устройства в ответ на посылку с идентификатором конца сообщения.

Если запрашиваемый выход занят, то запросы ожидают его освобождения.

Если хотя бы в одной из посылок сообщения обнаружена ошибка по четности или неправильный идентификатор, вырабатывается соответствующий признак. Он может быть выдан коммутатором по запросу диспетчера обменов через устройство унифицированного сопряжения внешних устройств или по запросу любого обслуживающего устройства.

Предмет изобретения

1. Информационно-вычислительная система, содержащая центральные процессоры, блоки памяти и периферийные процессоры, составляющие группу высокопроизводительных устройств, и внешние устройства, отличающаяся тем, что, с целью повышения производительности и надежности системы и экономии оборудования, она содержит устройство унифицированного сопряжения, объединяющее высокопроизводительные устройства и устройство унифицированного сопряжения, объединяющее внешние устройства.

2. Информационно-вычислительна система по п. 1, отличающаяся, тем, что устройство сопряжения высокопроизводительных устройств содержит шины данных, шины адресов отправителя и адресата, шины синхронизации и сеть коммутации на 2m направлений (m—количество разрядов адреса устройства, участвующего в обмене), состоящую из коммутаторов, имеющих l=3/2m направлений, при этом каждый коммутатор имеет для каждого направления блоки приема сообщений, входы которых соединены с шинами обмена, блоки синхронизации, блоки контроля по четности, блоки защиты, блоки преобразования адреса, блоки дешифрации, блоки очередности коммутации, регистры, блоки выдачи сообщений, выходы которых соединены с шинами обмена, блок работы с диспетчером, блок управления коммутацией, причем первые выходы блоков приема сообщений соединены с первыми входами каждого регистра, вторые выходы блоков приема сообщений соединены со входами соответствующих блоков синхронизации и блоков преобразования адреса, со входами блока работы с диспетчером и со входами соответствующих блоков защиты и блоков контроля по четности, выходы которых соединены с соответствующими входами блока работы с диспетчером, первый выход блока работы с диспетчером соединен с первыми входами блоков выдачи сообщений, вторые входы которых подключены к выходам соответствующих регистров, второй выход блока работы с диспетчером соединен с первыми входами блоков дешифрации, вторые и третьи входы которых соединены соответственно с выходами блоков преобразования адреса и блоков синхронизации, выходы каждого блока дешифрации соединены со входами каждого блока очередности коммутации, выходы которых соединены со входами блока управления коммутацией, выход блока управления коммутацией соединен со вторыми входами регистров.

3. Информационно-вычислительная система во п. 1 отличающаяся тем, что устройство унифицированного сопряжения внешних устройств содержит шины данных, шины идентификатора, шины контроля, шины синхронизации и сеть коммутаций на 2n+1 направлений (n — количество разрядов адреса внешнего устройства), состоящую из коммутаторов, имеющих p=3/(2n +1) направлений, каждый коммутатор имеет для каждого направления блоки приема посылок, входы которых соединены с шинами обмена, блоки контроля идентификатора, блоки контроля по четности, блоки формирования запросов, блоки выдачи посылок, выходы которых подключены к шинам обмена, схемы готовности, блок определения очередности, блок формирования коммутирующего байта, блок управления коммутацией, причем первые выходы каждого блока приема посылок соединены с первыми входами каждого блока выдачи посылок за исключением блоков одного направления, со входами соответствующих блоков контроля по четности и блоков контроля идентификаторов, с первой группой входов блока определения очередности, вторые выходы блоков приема посылок соединены с первыми входами соответствующих блоков формирования запросов, вторые входы которых соединены с выходами соответствующих блоков контроля во четности, третьи — с выходами соответствующих блоков контроля идентификаторов, четвертые входы блоков приема посылок соединены с выходами соответствующих схем готовности, выходы блоков приема посылок соединены со второй группой входов блока определения очередности, выход которого соединен со входом блока формирования коммутирующего байта, первый выход которого соединен со вторыми входами блоков выдачи посылок, а второй выход — со входом блока управления коммутацией, причем первый его выход подключен к схемам готовности, а второй — к третьим входам блоков выдачи посылок.

Материал помещен в музей 14.08.2009 года