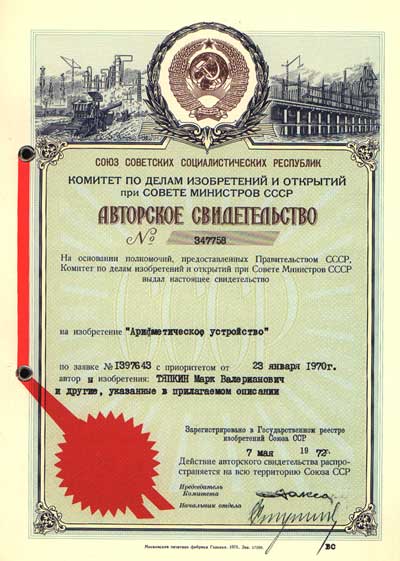

Арифметическое устройствои

Описание изобретения к авторскому свидетельству

Авторы изобретения: А. В. Аваев, В. С. Новизенцев и М. В. Тяпкин

Изобретение относится к области вычислительной техники, а именно, к арифметическим устройствам одноадресных вычислительных машин. Известны арифметические устройства (АУ), в которых операция сложения выполняется в два этапа: сначала вырабатывается двухрядный код, затем приводятся переносы и получается окончательный однорядный результат.

Приведение результата после каждой операции обуславливает непроизводительные затраты времени, если в последовательности выполняемых команд встречается нёсколько следующих друг за другом операций типа сложения, результаты которых не требуется записывать в память.

Цель изобретения — повышение быстродействия.

Цель достигается введением в схему АУ специальных цепей, производящих анализ типа операции, следующей за выполняемой в данный момент, и разрешающих выполнение следующей операции до окончания приведения результата выполняемой в данный момент операции в однорядный вид, если операция, следующая за выполняемой, не требует представления результата предыдущей в однорядном коде.

Для этого предлагаемое арифметическое устройство, содержащее входной регистр, соединенный с двухрядным сумматором, выход которого соединен с триггером окончания приведения результата, единичный выход которого соединен со входом схемы «И», блок буферных регистров команд, выход которого соединен со входом устройства управления операциями, триггер завершения операции, дополнительно содержит дешифратор операций, управляющий триггер и логические схемы «И» и «ИЛИ», второй выход блока буферных регистров соединен со входом дешифратора операций, выход которого соединен со входом управляющего триггера, единичным выходом подключенного ко второму входу первой схемы «И», а нулевым к первому входу второй схемы «И», выходы первой и второй схем «И» соединены со входами схемы «ИЛИ», выход которой соединен со входом триггера завершения операции.

На чертеже представлена блок-схема предлагаемого АУ.

Оно содержит двухрядный сумматор 1, входной регистр 2, устройство 3 управления операциями, кодовые шины 4 числа, двухвходовую схему «И» (триггер) 5, триггер 6 завершения операций, триггер 7 окончания приведения, управляющий триггер 8, дешифратор 9 операций, требующих обязательного окончания приведения, блок 10 буферных регистров предварительной выработки команд, двухвходовую схему «И» 11, схему «ИЛИ» 12.

Работает арифметическое устройство следующим образом.

Если за выполняемой в данный момент операцией следует записанная в буферных регистрах 10 арифметическая операция над содержимым сумматора и новым операндом, то эта операция начинается до начала приведения результата выполняемой в данный момент операции, причем эта следующая операция производится над новым операндом и результатом предыдущей операции, представленным в двухрядном коде.

При получении результата текущей операции в двухрядном коде устройство 8 разрешает дешифрацию следующей операции. Если следующая операция требует обязательного приведения (например, операция « Запись», для которой число должно быть представлено в однорядном коде), то триггер 8 устанавливается в положение «1» и дальнейшее выполнение операции происходит так же, как в известном устройстве.

Если вслед за выполняемой следует арифметическая операция типа сложения (вычитания), то триггер 8 остается в состоянии «0», разрешая через схемы 11 и 12 установку в «1» триггера 6 и начало следующей операции до окончания приведения результата предыдущей.

Предмет изобретения

Арифметическое устройство, содержащее входной регистр, соединенный с двухрядным сумматором, выход которого соединен с триггером окончания приведения результата, единичный выход которого соединен со входом схемы «И», блок буферных регистров команд, выход которого соединен со входом устройства управления операциями, триггер завершения операции, отличающееся тем, что, с целью повышения быстродействия, ено дополнительно содержит дешифратор операций, управляющий триггер и логические схемы «И» и «ИЛИ», второй выход блока буферных регистров соединен со входом дешифратора операций, выход которого соединен со входом управляющего триггера, единичным выходом подключенного ко второму входу первой схемы «И», а нулевым к первому входу второй схемы «И», выходы первой и второй схем «И» соединены со входами схемы «ИЛИ», выход которой соединен со входом триггера завершения операции.

Материал помещен в музей 25.02.2009