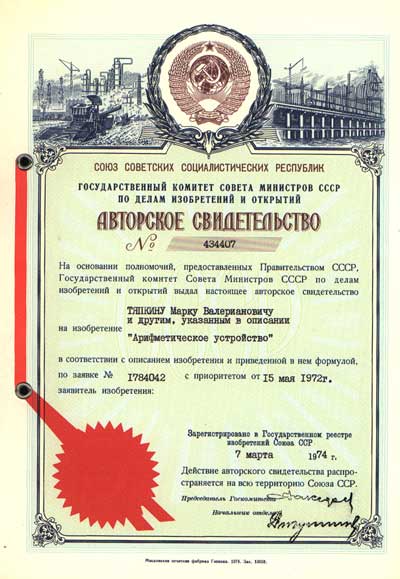

Арифметическое устройство

Описание изобретения к авторскому свидетельству

Авторы изобретения: А.В. Аваев, В.Л. Ли и М.В. Тяпкин

Изобретение относится к вычислительной технике, а именно к арифметическим устройствам (АУ) вычислительных машин.

Известны АУ с магистральной структурой, состоящие из дешифратора команд, адресуемых регистров, блока выборки операндов из адресуемых регистров и собственно арифметического блока, выполняющего над выбранными операндами заданную дешифратором команд операцию и посылающего результат в один из адресуемых регистров. Обычно, особенно в высокопроизводительных машинах, арифметический блок состоит из трех последовательных блоков — блока предварительной обработки операндов (выполняющего, например, выравнивание порядков при сложении чисел с плавающей занятой), блока основной обработки операндов (выполняющего, например, сложение мантисс чисел с плавающей занятой) и блока завершающей обработки (выполняющего, например, нормализацию результата после операций над числами с плавающей за пятой).

В таком АУ возникает необходимость задержки выборки операндов очередной команды из адресуемых регистров и, следовательно, задержка начала выполнения очередной команды до завершения записи в адресуемые регистры результата предыдущей команды. Это связано с тем, что возможны случаи, ког да в качестве операнда очередной команды должен быть использован результат предыдущей команды.

Целью настоящего изобретения является повышение производительности АУ с магистральной структурой путем ускорения начала выполнения последующей команды по отношению к моменту получения результата предыдущей команды.

На чертеже представлена схема предлагаемого АУ.

Оно содержит дешифратор 1 команд, последовательно включенные блоки 2—4 соответственно предварительной обработки операндов, основной обработки операндов, завершающей обработки результата, блок 5 адресуемых регистров и блок 6 выборки операндов. Один из входов блока 6 соединен с выходом блока 5 адресуемых регистров, другой — с выходом дешифратора команд, а выход — с входом блока 2 предварительной обработки операндов. В предлагаемое АУ введены добавочные блоки: блок 7 сравнения, второй блок 8 выборки операндов, третий блок 9 выборки операндов, адресный регистр 10 предварительной обработки, адресный регистр 11 основной обработки и адресный регистр 12 завершающей обработки. Кроме того, в блок 6 выборки операндов введен третий, запрещающий вход, соединенный с выходом блока 7 сравнения.

Цепи получения операндов из оперативной памяти, цепи записи результатов в оперативную память и цепи связи АУ с устройством управления вычислительной машины на чертеже не показаны, так как в предлагаемом АУ они не отличаются от аналогичных цепей известных АУ.

Работает предлагаемое АУ следующим образом.

При выборке операндов очередной команды в блок 2 на адресном регистре 10 устанавливается из дещифратора 1 команд номер адресуемого регистра, в который должен быть записан результат данной команды. При передаче операндов из блока 2 в блок 3 содержимое регистра 10 пересылается на регистр 11, а при передаче результата из блока 3 в блок 4 содержимое регистра 11 пересылается на регистр 12.

Выборка операндов следующей команды в блок 2 начинается сразу же после его освобождения от предыдущей команды, однако блок 7 сравнения, сравнивающий поступающие из дешифратора команд номера адресуемых регистров, из которых должны быть выбраны эти операнды, с содержимым адресных регистров 10, 11, 12, запрещает работу блока 6 выборки операндов, если операнд должен быть выбран из адресуемого регистра, номер которого содержится в одном из адресных регистров 10, 11 или 12. В этом случае операнд на вход блока 2 выбирается либо с выхода блока 3 (через второй блок 8 выборки операндов), либо с выхода блока 4 (через третий блок 9 выборки операндов), причем выборка операнда производится в момент появления соответствующего результата на выходе блока 3 или 4. Выборка операнда с выхода блока 3 производится только в тех случаях, когда в блоке 3 выполняется команда, не требующая завершающей обработки результата (например, типа пересылки из одного адресуемого регистра в другой, типа поразрядных логических операций и т. п.). В остальных случаях операнд в блок 2 выбирается с выхода блока 4.

Таким образом предлагаемое АУ имеет большую производительность по сравнению с известными АУ как в тех случаях, когда последующие команды не используют в качестве операндов результаты предыдущих команд (за счет одновременного выполнения различных стадий трех последовательных команд), так и в тех случаях, когда результат предыдущей команды используется в качестве операнда последующей (за счет исключения времени записи результата в адресуемый регистр, а при выполнении простейших команд — и за счет исключения времени прохождения результата через блок завершающей обработки результата).

Предмет изобретения

Арифметическое устройство, содержащее дешифратор команд, последовательно включенные блоки предварительной обработки операндов, основной обработки операндов, завершающей обработки результата, блок адресуемых регистров и блок выборки операндов, один из входов которого соединен с выходом блока адресуемых регистров, другой вход соединен с выходом дешифратора команд и выход - с входом блока предварительной обработки операндов, отличающееся тем, что, с целью повышения производительности, в него дополнительно введены блок сравнения, второй и третий блоки выборки операндов, первые входы которых соединены соответственно с выходами блоков основной и завершающей обработки операндов, вторые входы подключены к первому и второму выходам блока сравнения, а выходы объединены и подключены ко входу блока предварительной обработки операндов, а также последовательно соединенные адресные регистры предварительной, основной и завершающей обработки, выходы которых подключены соответственно к первому, второму и третьему входам блока сравнения, четвертый вход которого соединен с выходом дешифратора и со входом адресного регистра предварительной обработки, а третий выход подключен к запрещающему входу первого блока выборки операндов.

Материал помещен в музей 26.12.2008 года