Бистабильная схема

Описание изобретения к авторскому свидетельству

Авторы изобретения: В. А. Жуковский, В. Н. Лаут, В. С. Новизенцев, А. А. Соколов и М. В. Тяпкин

Предлагаемая схема относится к области вычислительной техники.

Известны схемы, обладающие двумя устойчивыми состояниями (бистабильные схемы или триггеры), в которых роль управляемой обратной связи выполняют диодные логические схемы.

Для известных бистабильных схем характерно наличие двух парафазных выходов, что облегчает их использование в логических схемах. Однако часто бистабильные схемы выполняют только функцию хранения информации, когда второго инверсного выхода не требуется.

Предлагаемая бистабильная схема с управляемой обратной связью имеет только один выход (прямой). Схема обладает высоким быстродействием и позволяет осуществить запоминание двоичной информации при использовании небольшого количества оборудования. Это достигнуто тем, что коллектор входного транзистора через подвешенный источник питания соединен с базой выходного транзистора, включенного по схеме с общим коллектором, эмиттер которого соединен с выходом схемы и через диодную схему совпадения обратной связи с эмиттером входного транзистора.

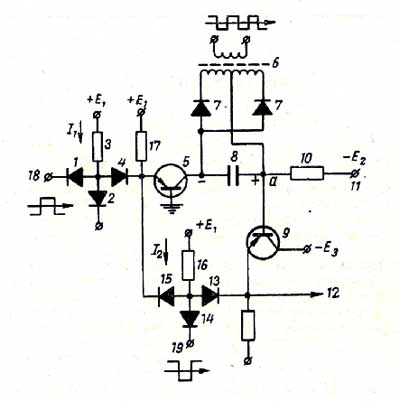

Предложенная схема приведена на чертеже.

Она состоит из входной диодной схемы сов. падения на диодах 1 и 2, аноды которых соединены с резистором 3 и через сборочный диод 4 с эмиттером входного транзистора, включенного по схеме с общей базой, коллектор которого через подвешенный источник питания, состоящий из трансформатора 6, диодов 7 и конденсатора 8, подключен к базе выходного транзистора 9 и через резистор 10 к источнику коллекторного питания 11 (—Е2 ). Эмиттер транзистора 9, включенного по схеме с общим коллектором, соединен с выходом схемы 12 и через диодную схему совпадения цепи обратной связи на диодах 13 и 15 и резисторе 14 — с эмиттером транзистора 5 и резистором 17.

Схема имеет два устойчивых состояния. Если потенциалы на входах 18 и 19 диодных схем совпадения таковы, что ток I1, задаваемый резистором 3, проходит через диод 2, а ток I2, задаваемый резистором 16, проходит через диод 14, то сборочные диоды 4 и 15 закрыты, и через транзистор 5 протекает лишь небольшой ток I3, задаваемый резистором 17. При этом потенциал в точке a , а следовательно, и на выходе 12 схемы в основном определяется величиной — Е2. Если теперь на вход 19 будет подан положительный потенциал, то состояние схемы не изменится, так как ток I 2 протекает через диод 11, и диод 15 по-прежнему заперт.

Если на все входы схемы совпадения на некоторое время поданы положительные потенциалы достаточной величины, то ток I1 переключается и течет через транзистор 5. При этом потенциал в точке a и на выходе схемы 12 становится положительным. Если в этот момент потенциал на входе 19 также положителен, то переключается и ток I2. Протекая через входной транзистор 5, он создает дополнительное падение напряжения на нагрузочном резисторе 10.

Если теперь входной сигнал будет снят, т. е. на один из входов, например 16, подан отрицательный потенциал, схема несмотря на это не меняет своего состояния, так как ток I2 по-прежнему протекает через транзистор 5, поддерживая положительный потенциал на выходе 12 схемы.

Таким образом, схема обеспечивает хранение двоичной информации.

Входной транзистор 5 благодаря наличию «подвешенного» источника напряжения работает в ненасыщенном режиме.

Уровни напряжений на выходе схемы достаточно стабильны, так как практически зависят лишь от Е2, токов I1 и I2 и величины резистора 10.

Предмет изобретения

Бистабильная схема, содержащая входные диодные схемы совпадения и диодную схему совпадения в цепи обратной связи, входной транзистор, включенный по схеме с общей базой, подвешенный источник питания и выходной транзистор, отличающаяся тем, что с целью повышения быстродействия и уменьшения количества оборудования, коллектор входного транзистора через подвешенный источник питания соединен с базой выходного транзистора, включенного по схеме с общим коллектором, эмиттер которого соединен с выходом схемы и через диодную схему совпадения обратной связи — с эмиттером входного транзистора.

Материал помещен в музей 26.11.2008 года