Устройство для умножения десятичных чисел

Описание изобретения к авторскому свидетельству

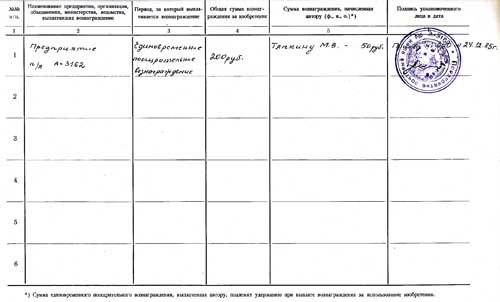

Авторы изобретения: М.В. Тяпкин, М.А. Головина, В.А. Ваканова и И.В. Волкова

Устройство для умножения десятичных чисел, содержащее регистры множимого, множителя и результата, множительный блок, блок суммирования, блок преобразования двоичного кода результата в десятичный и блок приведения десятичных переносов, отличающееся тем, что, с целью повышения быстродействия, в него введены блок формирования переносов, блок записи результатов и блок выборки байтов, причем блок выборки байтов содержит счетчики выборки байтов множимого, множителя и частичного произведения, коммутаторы байтов множимого, множителя и частичных произведений, регистры кодов множимого, множителя и частичных произведений, триггер, три группы элементов «И» и регистры цифр множимого, множителя и частичных произведений, множительный блок содержит умножители десятков и единиц регистры единиц и десятков, регистры, переносов единиц, десятков и сотен и регистры единиц и десятков частичного произведения, блок суммирования содержит трехвходовые сумматоры единиц и десятков, регистры суммы единиц, десятков и сотен и регистры переносов единиц и десятков, блок формирования переносов содержит двухвходовые сумматоры приведения переносов единиц и десятков, узлы формирования переносов сотен и десятков, регистры суммы единиц и десятков, регистры переносов единиц и десятков, регистры десятичного переноса единица десятков и сотен, блок преобразования двоичного кода результата в десятичный содержит преобразователи двоичного кода единиц и десятков в десятичный, формирователи десятичных переносов десятков и сотен, регистры суммы единиц и десятков, регистры десятичного переноса единиц, десятков и сотен, блок приведения десятичных переносов содержит сумматоры приведения десятичных переносов единиц и десятков и регистр результата, а блок записи результата содержит счетчик записи байтов результата и группу элементов «И», выходы которых соединены с входом регистра результата, выходы регистров множимого, множителя и результата соединены соответственно с информационными входами коммутаторов множимого, множителя и частичных произведений блока выборки байтов, управляющие входы которых соединены соответственно с информационными выходами счетчиков выборки байтов множимого, множителя и частичных произведений блока выборки байтов, выходы сброса которых, кроме выхода сброса счетчика выборки байтов множимого, соединены соответственно с первыми входами элементов «И», первой и второй групп блока выборки байтов, выход сброса счетчика выборки байтов множимого блока выборки байтов соединен с входом установки триггера блока выборки байтов, выход которого соединен с первыми входами. элементов «И», третьей группы блока выборки байтов, вторые входы элементов «И» первой, второй и третьей групп блока выборки байтов соединены соответственно с выходами регистров кодов множителя частичных произведений и множимого блока выборки байтов, а выходы — с входами регистров цифр множителя, частичных произведений и множимого блока выборки байтов, выходы старшей и младшей цифр регистра цифр множимого блока выборки байтов соединены соответственно с первыми входами умножителей единиц и десятков множительного блока, вторые входы которых соединены с выходом регистра цифр множителя блока выборки байтов, выходы старшей и младшей цифр регистра цифр частичного произведения которого соединены соответственно с входами регистров десятков и единиц частичного произведения множительного блока, первый выход умножителя десятков которого соединен с входом регистра переносов сотен множительного блока, выход которого соединен с входом регистра суммы сотен блока суммирования, выход которого соединен с входом регистра переносов единиц множительного блока, второй выход умножителя десятков которого соединен с входом регистра десятков множительного блока, вход регистра переносов десятков которого соединен с первым выходом умножителя единиц множительного блока, второй выход которого соединен с входом регистра единиц множительного блока, выходы регистров единиц, переносов единиц и единиц частичного произведения которого соединены соответственно с входами трехвходового сумматора единиц блока суммирования, входы трехвходового сумматора десятков которого соединены соответственно с выходами регистров десятков переносов десятков и десятков частичного произведения множительного блока, выходы суммы трехвходовых сумматоров единиц и десятков блока суммирования соединены соответственно входами регистров суммы единиц и десятков блока суммирования, входы регистров переносов единиц и десятков которого соединены соответственно с выходами переноса трехвходовых сумматоров единиц и десятков блока суммирования, выходы регистров суммы десятков и единиц которого соединены соответственно с первыми входами узла формирования переносов сотен и двухвходового сумматора приведения переносов десятков и узла формирования переносов десятков и двухвходового сумматора приведения переносов единиц блока формирований переносов, вторые входы которых соединены соответственно с выходами регистров переносов десятков и единиц блока суммирования, выходы узлов формирования переносов сотен десятков блока формирования переносов соединены соответственно с входами регистров десятичного переноса сотен, и десятков блока формирования переносов, выход регистра переноса сотен которого соединен с первым входом преобразователя двоичного кода десятков в десятичный и входом регистра десятичного переноса сотен блока преобразования двоичного кода результата в десятичный, второй и третий входы преобразователя двоичного кода десятков в десятичный которого соединены соответственно с выходами регистров переносов и суммы десятков блока формирования переносов, входы которых соединены соответственно с выходами переноса и суммы двухвходового сумматора приведения переносов десятков блока формирования переносов выход узла формирования переносов десятков которого соединен с входом регистра десятичного переноса блока формирования переносов, выход которого соединен с первыми входами преобразователя двоичного кода единиц в десятичный формирователя десятичного переноса десятков блока преобразования двоичного кода результата в десятичный, вторые входы которых соединены с выходом регистра суммы единиц блока формирования переносов, вход которого соединен с выходом суммы двухвходового сумматора приведения переносов единиц блока формирования переносов, выход переноса которого соединен с входом регистра переносов единиц блока формирования переносов, выход которого соединен с третьим входом преобразователя двоичного кода единиц в десятичный блока преобразования двоичного кода результата в десятичный, третий вход формирователя десятичного переноса десятков и вход регистра десятичного переноса единиц которого соединены с выходом регистра десятичного переноса единиц блока формирования переносов, вход которого соединен с выходом формирователя десятичного переноса сотен блока преобразования двоичного кода результата в десятичный, первый вход которого соединен с выходом регистра десятичного переноса сотен блока преобразования двоичного кода результата в десятичный, а второй и третий входы — с входами сумматора приведения десятичных переносов десятков блока приведения десятичных переносов и выходами регистров суммы и десятичного переноса десятков блока преобразования двоичного кода результата в десятичный соответственно, входы которых соединены соответственно с выходами преобразователей двоичного кода десятков и переносов в десятичный блока преобразования двоичного кода результата в десятичный, выход преобразователя двоичного кода единиц в десятичный которого соединен с входом регистра суммы ёдиниц блока преобразования двоичного кода результата в десятичный, выходы регистров суммы и десятичного переноса единиц которого соединены с входами сумматора приведения десятичного переноса единиц блока приведения десятичных переносов, выходы сумматоров приведения десятичных переносов единиц и дёсятков которого соединены соответственно с входами младшей и старшей тетрад регистра результата блока приведения десятичных переносов, выход которого соединен с первыми входами элементов «И» группы блока записи результата, вторые входы которых соединены выходом счетчика записи байтов результата блока записи результата.

Изобретение относится к вычислительной технике. Целью изобретения является повышение быстродействия.

На чертеже представлена блок-схема устройства для умножения десятичных чисел.

Устройство содержит регистры множимого 1, множителя 2, результата 3, блок 4 выборки байтов, множительный блок 5 блок 6 суммирования, блок 7 формирования переносов, блок преобразования двоичного кода результата в десятичный, блок 9 приведения десятичных переносов, блок 10 записи результата.

Блок 4 выборки байтов содержит счетчики выборки байтов множимого 11, множителя 12 и частичного произведения 13, коммутаторы байтов множимого 14, множителя 15 и частичного произведения 16, регистры кодов множимого 17, множителя 18 частичных произведений 19, триггер 20, три группы элементов «И» 21 — 23, регистры цифр множимого 24, множителя 25 и частичных произведений 26.

Множительный блок 5 содержит умножители десятков 27 и единиц 28, регистры единиц 29 и десятков 30, регистры переносов единиц 31, десятков 32 и сотен 33, регистры единиц 34 и десятков 35 частичного произведения.

Блок 6 суммирования содержит трехвходовые сумматоры единиц 36 и десятков 37, регистры суммы единиц 38, десятков 39 и сотен 40, регистры переносов ёдиниц 41 и десятков 42.

Блок 7 формирования переносов содержит двухвходовые сумматоры приведения переносов единиц 43 и десятков 44, узлы формирования переносов сотен 45 и десятков 46, регистры суммы единиц 47 и десятков 48, регистры переносов единиц 49 и десятков 50, регистры десятичного перенос единиц 51, десятков 52 и сотен 53.

Блок 8 преобразования двоичного кода результата в десятичный содержит преобразователи двоичного кода единиц 54 и десятков 55 в десятичный, формирователи десятичных переносов десятков 56 и сотен 57, регистры суммы единиц 58 и десятков 59, регистры десятичного переноса единиц 60, десятков 61 и сотен 62.

Блок 9 приведения десятичных переносов содержит сумматоры десятичных переносов единиц 63 и десятков 64, регистр 65 результата.

Блок 10 записи результата содержит счетчик 66 записи байтов результата и группу элементов «И» 67.

Умножение проводится последовательно. Каждый такт на входы умножителей поступает следующий байт множимого.

Пропускная способность устройства — байт за такт — достигается благодаря умножителям, дающим сразу на вход блока 6 суммирования произведения двух десятичных цифр множимого на десятичную цифру множителя (две цифры произведения и две цифры переноса в следующий десятичный разряд).

Счетчик 11 выборки байтов множимого — трехразрядный, байты в нем выбираются последовательно, начиная с правого (пятого). В начале каждого цикла на счетчик заносится код “ 5” . Счетчик работает в режиме счета от 5 до 0 и имеет шесть позиционных выходов, каждый из которых представляет собой триггер.

Счетчик 12 выборки байтов множителя — четырехразрядный. Три старших разряда управляют выборкой байта множителя аналогично счетчику 11, а младший разряд выбирает цифру в байте. Выборка каждой цифры сопровождается вычитанием 1 из кода счетчика 12.

Счетчик 13 выборки байтов частичного произведения имеет конструкцию и работает аналогично счетчику 11.

Коммутаторы байтов множимого 14, множителя 15 и частичных произведений 16 состоят каждый из шести групп вентилей (по 8 вентилей в каждой).

Регистры кодов множимого 17, множителя 18, частичных произведений 19 предназначены для хранения кода на этих регистрах до переключения счетчиков выборки байтов.

Группа элементов «И» 21 предназначена для прямой передачи байта и со сдвигом вправо на одну десятичную цифру множимого.

Триггер 20 служит как признак сдвига, который перебрасывается каждый раз после обнуления счетчика 11.

Группы элементов «И» 22 и 23 предназначены для прямой передачи кодов множителя и частичных произведений соответственно.

Регистр цифр множимого 24 — восьмиразрядный и предназначен для передачи последовательности из двух десятичных цифр со сдвигом на одну цифру.

Регистр цифр множителя 25 — четырехразрядный и предназначен для передачи по одной десятичной цифре множителя с регистра 18.

Регистр частичных произведений 26 аналогичен регистру 24.

Умножители 27 и 28 построены на комбинационных схемах на выходах которых сразу образуется десятичный код произведения двух цифр множимого на одну цифру множителя и которые выполнены по принципу перебора всевозможных сочетаний цифр множимого и множителя.

Регистр переносов единиц 31 предназначен для передачи десятичного переноса из предыдущего байта.

Регистры переносов десятков 32 и сотен 33 предназначены для передачи десятичных переносов с умножителей 28 и 29 соответственно.

Трехвходовые сумматоры единиц 36 и десятков 37 служат для образования двоичной суммы в двухрядном коде, которая помещается на соответствующие регистры суммы и регистры переносов.

Узлы формирования переносов сотен 45 и десятков 46 представляет собой логические схемы, которые анализируют коды на регистрах суммы 38, 39 и переноса 41, 42. Если код на выходе регистров >= 10, то возникают признаки переноса на регистрах 52, 53 в следующий десятичный разряд. На вход 1—го разряда регистра 52 подключен 12-входовой элемент «ИЛИ», объединяющий 12 элементов «И», на входы которых подключены выходы регистров 38 и 41 в соответствии с табл. 1. Если код на выходе регистров >=20, то подключения по 2—му разряду регистра 52 происходит в соответствии с табл. 2.

Знак Х в разрядах регистров 38 и 41 означает, что для данной схемы «И» допустим любой код в этих разрядах, т.е. выходы этих разрядов к схеме «И» не подключаются.

На входы регистра десятичного переноса сотен 53 подключены аналогично табл. 1 и 2 схемы «И» — «ИЛИ», объединяющие коды с регистров 39 и 42.

Регистры 47 и 48 — четырехразрядные, младшие три разряда которых содержат двоичный код, полученный в результате приведения переносов младших трех разрядов регистров 38, 41 и 39, 42. Четвертый разряд регистров 47 и 48 получен в результате полного приведения кодов регистров 38, 41 и 39, 42 и содержит “ 1” , если окончательный результат равен 8 или 9 и формируется нестандартной частью сумматоров приведения 43 и 44, которая представляет собой 12-входовой элемент «ИЛИ», объединяющий 12 элементов «И», на входы которых поданы выходы регистров 38, 41 и 39, 42 в соответствии с табл. 3.

Регистры переноса 51, 52 и 53 и представляют собой двухразрядные регистры. Так как при сложении трех десятичных цифр сумма не может превышать 27, то перенос в следующий десятичный разряд может быть либо 1, либо 2.

Преобразователь 54 двоичного кода единиц в десятичный представляет собой схему, которая из приведенного кода двоичной суммы вычитает 10 или 20, если был признак переноса в следующий двоичный разряд, т.е на регистре 52 был код 01 или 1Х.

Преобразователь 55 аналогичен преобразователю единиц 54.

На четырехразрядных регистрах 58 и 59 образуется десятичный код пары цифр.

Формирователь десятичного переноса десятков 56 схема учитывает возможность возникновения десятичного переноса в случае, если на регистре 47 была цифра 8 или 9 и пришел перенос из предыдущего десятичного разряда, и работает в соответствии с табл. 4.

Формирователь 57 аналогичен формирователю 56.

Сумматоры 63 и 64 построены на диодных схемах, на выходе которых может быть код от 0 до 9.

Сумматор приведения десятичных переносов единиц 63 представлен в виде табл. 5. Сумматор 64 имеет такую же схему.

Регистр результата б5 предназначен для хранения результата, причем младшая цифра результата (единицы) помещается в правую регистра 65, старшая цифра (десятки) — в левую тетраду регистра.

Счетчик записи байтов результата 66 аналогичен счетчикам выборки байтов 11, 12 и 13.

Устройство работает следующим образом.

Начиная с младшего (пятого) байта множимое и множитель с регистров 1 и 2 выбирают на соответствующие регистры 17 и18 и затем байт множимого помещается на восьмиразрядный регистр 24. Каждый такт выбирается один байт множимого.

Цифра (тетрада) множителя помещается на регистр 17 и хранится там, пока все байты множимого не будут помножены на эту цифру. Затем выбирается следующая цифра из этого байта и процедура повторяется. После умножения на две цифры множителя счетчик выборки 12 переключается на новый байт.

Старшая цифра (тетрада) множимого 24 поступает на вход умножителя десятков 27, а младшая — на вход умножителя единиц 28. Цифра (тетрада) множителя поступает на входы обоих умножителей. Полученное на выходе умножителей 27 и 28 произведение суммируется с помощью трехвходовых сумматоров 36 и 37 с соответствующим десятичным разрядом частичного произведения и с переносом из предыдущего десятичного разряда.

Полусумма и перенос с выхода блока суммирования поступают на вход блока формирования десятичных переносов, где с помощью сумматоров 43 и 44 производится частичное приведение двоичных переносов.

Одновременно производится анализ результата на выходе блока суммирования. Если результат больше или равен 10, возникает признак переноса в следующий десятичный разряд и на регистрах 52 и 53 записывается код 01 (для 10) или 10 (для двадцати).

Полученный на выходе блока 7 результат преобразуется в десятичный код в блоке 8. Если был признак десятичного переноса в десятки, то преобразователь единиц 54 производит вычитание кода 10 или 20 из приведенной суммы единиц, а преобразователь десятков 55 вычитает 10 или 20 из суммы десятков, если был признак, переноса сотен на регистре 53.

Преобразованная в десятичный код сумма складывается с десятичным переносом из предыдущего разряда в блоке 9.

Сумматор 63 складывает код регистра суммы единиц 58 с десятичным переносом из предыдущего байта, находящегося на регистре 60.

Сумматор 64 складывает код регистра суммы десятков 58 с десятичным переносом из разряда единиц, находящегося на регистре 61. В регистр 65 помещается частичное произведение двух цифр множимого на одну цифру множителя. Произведение побайтно записывается в регистр результата 3, начиная с пятого байта. Счетчик записи 66 указывает номер байта, в который надо поместить очередное произведение.

После умножения на две цифры множителя очередное частичное произведение записывается со сдвигом на один байт. Для этого счетчик записи 66 устанавливается в новое начальное положение. Окончательный результат получается на регистре 3, когда все цифры множимого будут помножены на все цифры множителя.

Материал помещен в музей 04.03.2009 года