Устройство управления вычислительной машины

Описание изобретения к авторскому свидетельству

Авторы изобретения: А. В. Аваев, В. Л. Ли и М. В. Тяпкин

Изобретение относится к области вычислительной техники и может быть использовано для управления выполнением команд электронных вычислительных машин.

Известно устройство управления вычислительной машины, содержащее схемы готовности сумматора и входного регистра сумматора, коммутатор операций сумматора, регистр операций сумматора, дешифратор, элементы «И» и «ИЛИ», регистр команд обработки, схему сравнения адресов, адресуемый регистр, общий регистр команд, соединенные таким образом, что выход каждого триггера общего регистра команд соединен через двухходовые элементы «И» с входами соответствующих триггеров регистра команд обработки. Кроме того, выходы триггеров кода операции общего регистра команд связаны с входом дешифратора, первый выход которого соединен со вторыми входами элементов «И» на входе регистра команд обращений к памяти.

Недостатками известного устройства является, во-первых, то, что выполнение команд загрузки приводит к занятию времени арифметического устройства. Во-вторых, выполнение команды загрузки может значительно задержаться из-за ожидания операнда из памяти, В этом случае арифметическое устройство не может выполнять последующие арифметические команды, даже если они не используют регистр, указанный в команде загрузки. В третьих, команды загрузки, попадая в буфер команд арифметического устройства, сокращают количество арифметических команд, содержащихся в буфере. Это увеличивает сред- нее время выполнения команд в арифметическом устройстве.

Целью изобретения является повышение производительности вычислительной машины путем устранения названных недостатков.

Это достигается тем, что в устройство введен регистр команд обращений к памяти, все триггеры регистра команд соединены с первой группой входов схемы сравнения, а первый выход дешифратора через отдельные двухвходовые элементы «И» соединен с входами обоих триггеров установки блокировки регистра команд обработки, а через соответствующие двухвходовые элементы «И» и трехвходовые элементы «ИЛИ» первой группы соединен с единичными входами триггеров блокировки считывания адресуемого регистра. Вторые входы элементов «И», соединенные выходами со входами триггеров установки блокировки первого адреса, установки блокировки второго адреса и единичными входами триггеров блокировки считывания, соединены соответственно с первой, третьей и пятой группами выходов схемы сравнения адресов. Второй выход дешифратора подключен ко вторым входам элементов «И», соединенных выходами со входами триггеров кода операции первого адреса, второго адреса, через отдельные двухвходовые элементы «И» подключен ко входам обоих триггеров исключения из сравнения регистра команд обработки. Вторые входы элементов «И», соединенных выходами со входами триггеров исключения из сравнения первого адреса и второго адреса, соединены соответственно со второй и четвертой группами выходов схемы сравнения адресов. При этом выходы каждого триггера регистра команд обработки подключены ко второй группе входов схемы сравнения адресов. Кроме того, выходы триггеров кода операции регистра команд обработки соединены со входом коммутатора операций сумматора через отдельные двухвходовые элементы «И», вторые входы которых соединены с нулевым выходом триггера блокировки считывания адресуемого регистра. Выходы триггеров первого и второго адресов регистра команд обработки соединены со входным регистром сумматора и схемой готовности входного регистра сумматора через отдельные трехвходовые элементы «И» и соответственно адресам через первые и вторые входы отдельных элементов «ИЛИ». Вторые входы каждого из элементов «И» подключены к выходам триггеров адресуемого регистра, а третьи входы каждого из элементов «И» соединены с нулевым выходом триггера блокировки считывания адресуемого регистра, выходы триггеров установки блокировок первого и второго адреса связаны соответственно через отдельные двухвходовые элементы «И» со вторыми и третьими входами отдельных элементов «ИЛИ» первой группы. Ко вторым входам элементов «И» подключены соответственно выходы схем готовности сумматора и входного регистра сумматора, при этом выходы каждого триггера коммутатора операций сумматора, входного регистра сумматора и схемы готовности входного регистра сумматора соединены со входами соответствующих триггеров регистра операций сумматора, сумматора и схемы готовности сумматора, а выходы каждого триггера кода операций, первого и второго адресов регистра команд обращений к памяти соединены через отдельные двухвходовые элементы «И» со входами оперативного запоминающего устройства. Вторые входы элементов «И» подключены к единичному выходу триггера блокировки считывания адресуемого регистра, выход оперативного запоминающего устройства связан через отдельные двухвходовые элементы «И» со входами адресуемого регистра и нулевым входом триггера блокировки считывания из него, причем вторые входы элементов «И» соединены с выходами триггеров первого адреса регистра команд обращений к памяти.

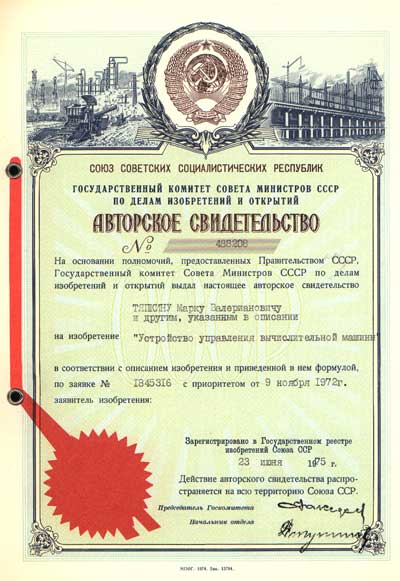

На чертеже изображена функциональная схема устройства управления вычислительной машины.

Оно содержит триггеры кода операций 1 общего регистра команд, триггеры первого адреса 2 регистра команд, триггеры второго адреса 3 регистра команд, дешифратор 4, схему сравнения адресов 5, двухвходовые элементы «И» 6—15, триггеры кода операций 16 регистра команд обращений к памяти, триггеры первого адреса 17 регистра команд обращений к памяти, триггеры второго адреса 18 регистра команд обращений к памяти, триггеры кода операций 19 регистра команд обработки, триггеры первого адреса 20 регистра команд обработки, триггеры второго адреса 21 регистра команд обработки, триггер 22 установки блокировки первого адреса регистра команд обработки, триггер 23 исключения из сравнения первого адреса регистра команд обработки, триггер 24 установки блокировки второго адреса регистра команд обработки, триггер 25 исключения из сравнения второго адреса регистра команд обработки, двухвходовые элементы «И» 26—28, память 29, двухвходовые элементы «И» 30—34, схему готовности сумматора 35, сумматор 36, регистр операций сумматора 37, трехвходовой элемент «ИЛИ» 38, схему готовности входного регистра сумматора 39, входной регистр 40 сумматора, коммутатор операций сумматора 41, адресуемый регистр 42, триггер 43 блокировки считывания из адресуемого регистра, двухвходовые элементы «ИЛИ» 44 и 45, трехвходовые элементы «И» 46—49 и двухвходовый элемент «И» 50.

Для простоты на чертеже изображен один адресуемый регистр и по одному регистру буфера обращений к памяти и буфера команд обработки (в реальных машинах число регистров каждого типа больше одного и зависит от соотношения скоростей арифметического и запоминающего устройств). Количество регистров разных типов не обязательно должно совпадать. При увеличении регистров каждый из них должен иметь на входе и выходе все элементы «И», «ИЛИ», показанные для одного регистра. Будем считать, что используется двухадресная система команд.

Общий регистр команд, регистр обращёний к памяти, регистр команд обработки содержат триггеры кода операции 1, 16 и 19, триггеры первого 2, 17 и 20 и второго 3, 18 и 21 адресов, соответственно. Адресуемый регистр 42 имеет триггер 43 блокировки считывания из регистра. Если триггер 43 блокировки считывания находится в состоянии «1», то разрешается обращение к памяти 29 и загрузка адресуемого регистра 42. Если триггер 43 находится в состоянии «0», разрешается считывание из регистра 42 на входной регистр 40 сумматора. Регистр команд обработки имеет четыре триггера. Триггеры 22 и 24 служат для хранения признаков установки блокировок соответственно по первому и второму адресам, а триггеры 23 и 25 для хранения признаков исключения из сравнения по первому и второму адресам.

Эти признаки обеспечивают начало выпол65 нения команды загрузки после того, как последняя из впереди идущих по программе арифметических команд, обращающихся к рассматриваемому адресуемому регистру, считает содержимое регистра в сумматор. Кроме того, признаки обеспечивают начало выполнения арифметической команды после последней из впереди идущих по программе загрузок.

Правильная последовательность команд с совпадающими адресами обеспечивается следующим образом.

Оба адреса любой команды, появившейся на общем регистре команд, сравниваются схемой сравнения адресов 5 с каждым из адресов регистра команд обработки. Если совпадение не обнаружено, то дешифратор 4 передает команду загрузки в регистр обращений к памяти, а арифметическую команду — в регистр команд обработки. При этом команда загрузки устанавливает в состояние «1» триггер 43 блокировки считывания из адресуемого регистра и запрещает считывание из него в сумматор, а арифметическая команда не устанавливает признаков. Сброс триггера 43 в состояние «0» осуществляется в момент загрузки адресуемого регистра.

При совпадении адресов направление передачи команды также определяется дешифратором 4. Возможны четыре варианта последовательностей команд, проходящих через общий регистр команд. Команда загрузки не устанавливает предыдущей команде загрузки с совпадающим адресом регистра 42 признаков, но выполняться она начнет после окончания предыдущей загрузки, так как заполнение регистра обращений к памяти и выборка из него происходит последовательно. Команда загрузки, следующая за арифметической командой с совпадающим адресом регистра 42, ставит ей признак установки блокировки совпадающего адреса. Триггер этого признака вместе со схемой готовности сумматора 35 (совпадение с первым адресом) или со схемой готовности входного регистра сумматора 39 (совпадение с вторым адресом) устанавливает триггер 43 блокировки считывания адресуемого регистра 42 и разрешает загрузку регистра 42 после того, как последняя арифметическая команда, использующая этот регистр, считывает его содержимое в сумматор.

Арифметическая команда ставит предыдущей арифметической команде с совпадающим адресом признак исключения из сравнения этого адреса. Таким образом, в сравнении всегда участвует последняя арифметическая команда из группы команд с совпадающими адресами, использующая рассматриваемый адресуемый регистр. Если перед арифметической командой была команда загрузки с совпадающим адресом регистра 42, то арифметическая команда не ставит признаков, но ее выполнение разрешается после сброса в состояние «0» соответствующего триггера 43 блокировки считывания, т. е. после загрузки регистра 42.Формула изобретения

Устройство управления вычислительной машины, содержащее схемы готовности сумматора и входного регистра сумматора, коммутатор операций сумматора, регистр операций сумматора, дешифратор, элементы «И» и «ИЛИ», регистр команд обработки, схему сравнения адресов, адресуемый регистр, общий регистр команд, соединенные таким образом, что выход каждого триггера общего регистра команд соединен через двухвходовые элементы «И» с входами соответствующих триггеров регистра команд обработки, кроме того, выходы триггеров кода операции общего регистра команд связаны с входом дешифратор а, первый выход которого соединен со вторыми входами элементов «И» на входе регистра команд обращений к памяти, отличающееся тем, что, с целью повышения производительности вычислительной машины, дополнительно введен регистр команд обращений к памяти, все триггеры регистра команд соединены с первой группой входов схемы сравнения, а первый выход дешифратора через отдельные двухвходовые элементы «И» соединен с входами обоих триггеров установки блокировки регистра команд обработки, а через соответствующие двухвходовые элементы «И» и трехвходовые элементы «ИЛИ» первой группы соединен с единичными входами триггеров блокировки считывания адресуемого регистра, причем вторые входы элементов «И» соединенные выходами со входами триггеров установки блокировки первого адреса, установки блокировки второго адреса и единичными входами триггеров блокировки считывания, соединены соответственно с первой, третьей и пятой группами выходов схемы сравнения адресов, второй выход дешифратора подключен ко вторым входам элементов «И», соединенных выходами со входами триггеров кода операций, первого адреса, второго адреса, через отдельные двухвходовые элементы «И» подключен ко входам обоих триггеров исключения из сравнения регистра команд обработки, причем вторые входы элементов «И», соединенных выходами со входами триггеров исключения из сравнения первого адреса и второго адреса, соединены соответственно со второй и четвертой группами выходов схемы сравнения адресов, при этом выходы каждого триггера регистра команд обработки подключены ко второй группе входов схемы сравнения адресов, кроме того, выходы триггеров кода операции регистра команд обработки соединены со входом коммутатора операций сумматора через отдельные двухвходовые элементы «И», вторые входы которых соединены с нулевым выходом триггера блокировки считывания адресуемого регистра, выходы триггеров первого и второго адресов регистра команд обработки соединены со входным регистром сумматора и схемой готовности входного регистра сумматора через отдельные трехвходовые элементы «И» и соответственно адресам через первые и вторые входы отдельных элементов «ИЛИ», причем вторые входы каждого из элементов «И» подключены к выходам триггеров адресуемого регистра, а третьи входы каждого из элементов «И» соединены с нулевым выходом триггера блокировки считывания адресуемого регистра, выходы триггеров установки блокировок первого и второго адресов связаны соответственно через отдельные двухвходовые элементы «И» со вторыми и третьими входами отдельных элементов «ИЛИ» первой группы, причем ко вторым входам элементов «И» подключены соответственно выходы схем готовности сумматора и входного регистра сумматора, при этом выходы каждого триггера коммутатора операций сумматора, входного регистра сумматора и схемы готовности входного регистра сумматора соединены со входами соответствующих триггеров регистра операций сумматора, сумматора и схемы готовности сумматора, а выходы каждого триггера кода операции, первого и второго адресов регистра команд обращений к памяти соединены через отдельные двухвходовые элементы «И» со входами оперативного запоминающего устройства, причем вторые входы элементов «И» подключены к единичному выходу триггера блокировки считывания адресуемого регистра, выход оперативного запоминающего устройства связан через отдельные двухвходовые элементы «И» со входами адресуемого регистра и нулевым входом триггера блокировки считывания из него, причем вторые входы элементов «И» соединены с выходами триггеров первого адреса регистра команд обращений к памяти.

Материал помещен в музей 10.02.2009 года